RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 161

Dec 10, 2015

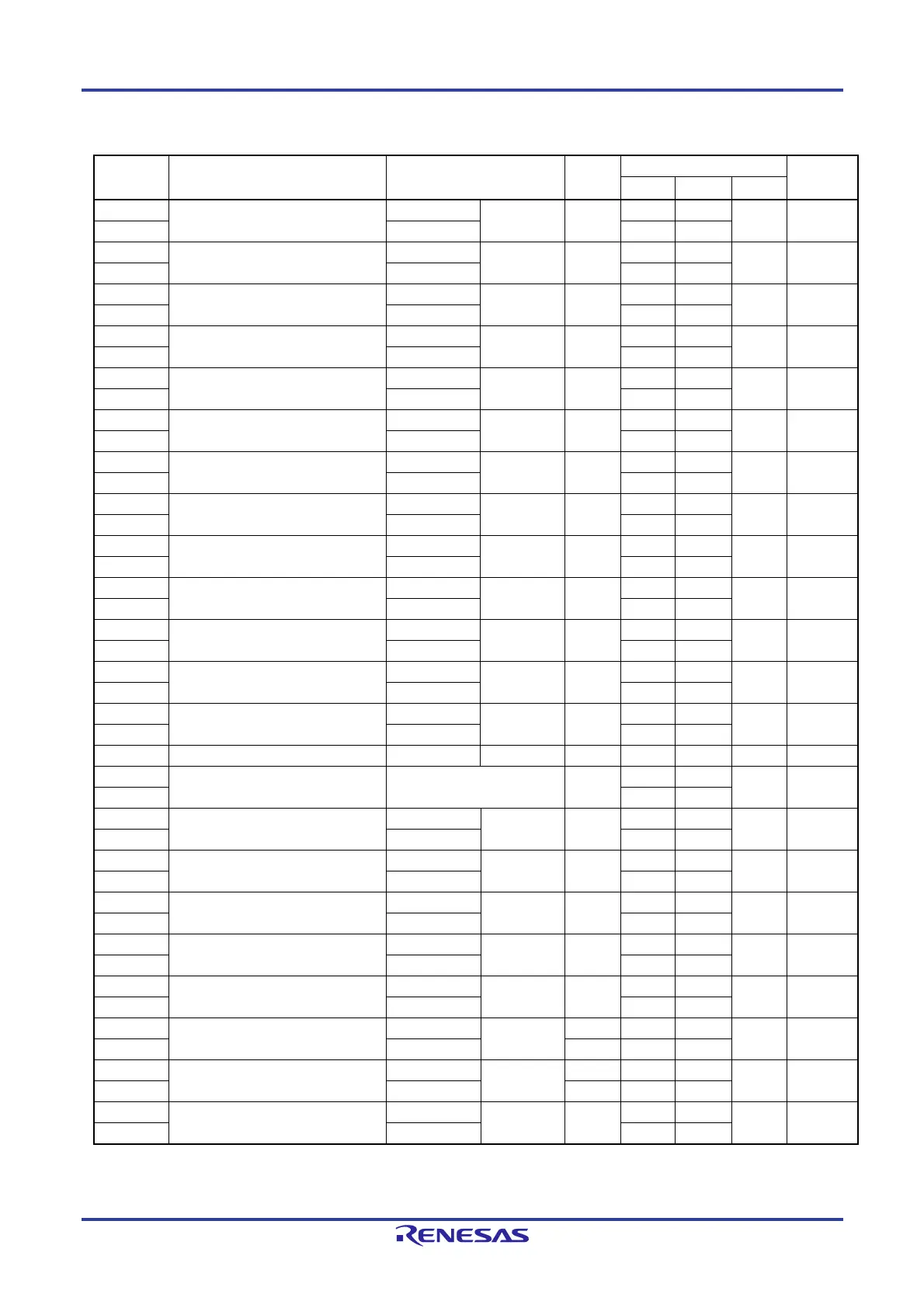

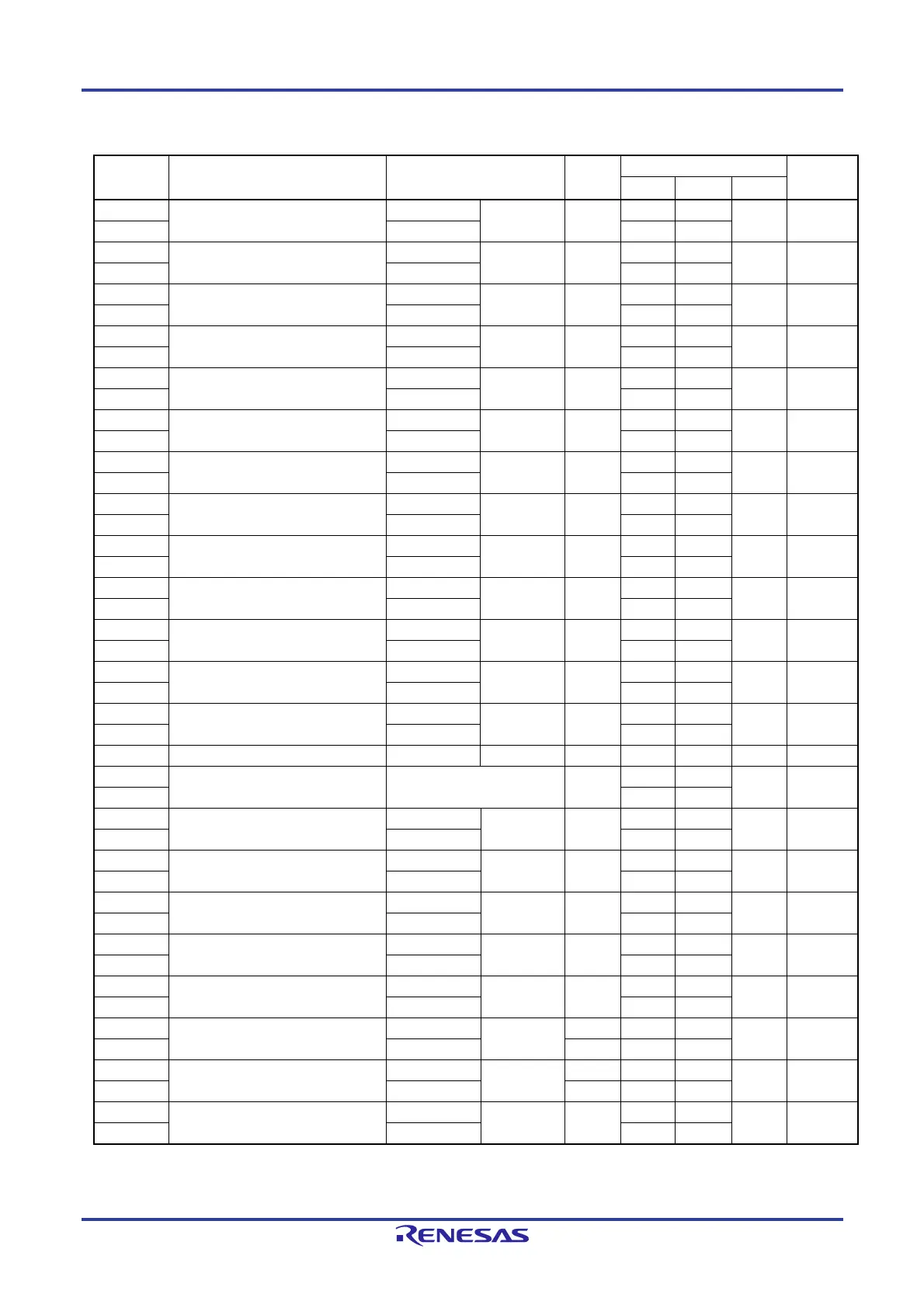

Table 3-6. Extended SFR (2nd SFR) List (10/32)

Address Special Function Register (2nd SFR)

Name

Symbol R/W Manipulable Bit Range After reset

1-bit 8-bit 16-bit

F0300H CAN0 bit configuration register L C0CFGLL C0CFGL R/W – √ √ 0000H

F0301H C0CFGLH – √

F0302H CAN0 bit configuration register H C0CFGHL C0CFGH R/W – √ √ 0000H

F0303H C0CFGHH – √

F0304H CAN0 control register L C0CTRLL C0CTRL R/W – √ √ 0005H

Note

F0305H C0CTRLH – √

F0306H CAN0 control register H C0CTRHL C0CTRH R/W – √ √ 0000H

F0307H C0CTRHH – √

F0308H CAN0 status register L C0STSLL C0STSL R – √ √ 0005H

Note

F0309H C0STSLH – √

F030AH CAN0 status register H C0STSHL C0STSH R – √ √ 0000H

F030BH C0STSHH – √

F030CH CAN0 error flag register L C0ERFLLL C0ERFLL R/W – √ √ 0000H

F030DH C0ERFLLH – √

F030EH CAN0 error flag register H C0ERFLHL C0ERFLH R – √ √ 0000H

F030FH C0ERFLHH – √

F0322H CAN global configuration register L GCFGLL GCFGL R/W – √ √ 0000H

F0323H GCFGLH – √

F0324H CAN global configuration register H GCFGHL GCFGH R/W – √ √ 0000H

F0325H GCFGHH – √

F0326H CAN global control register L GCTRLL GCTRL R/W – √ √ 0005H

Note

F0327H GCTRLH – √

F0328H CAN global control register H GCTRHL GCTRH R/W – √ √ 0000H

F0329H GCTRHH – √

F032AH CAN global status register GSTSL GSTS R – √ √ 000DH

Note

F032BH GSTSH – √

F032CH CAN global error flag register GERFLL – R/W – √ – 00H

F032EH CAN timestamp register GTSC R – – √ 0000H

F032FH – –

F0330H CAN receive rule number

configuration register

GAFLCFGL GAFLCFG R/W – √ √ 0000H

F0331H GAFLCFGH – √

F0332H CAN receive buffer number

configuration register

RMNBL RMNB R/W – √ √ 0000H

F0333H – – –

F0334H CAN receive buffer receive complete

flag register

RMND0L RMND0 R/W – √ √ 0000H

F0335H RMND0H – √

F0338H CAN receive FIFO control register 0 RFCC0L RFCC0 R/W – √ √ 0000H

F0339H RFCC0H – √

F033AH CAN receive FIFO control register 1 RFCC1L RFCC1 R/W – √ √ 0000H

F033BH RFCC1H – √

F0340H CAN receive FIFO status register 0 RFSTS0L RFSTS0 R/W – √ √ 0001H

Note

F0341H RFSTS0H R – √

F0342H CAN receive FIFO status register 1 RFSTS1L RFSTS1 R/W – √ √ 0001H

Note

F0343H RFSTS1H R – √

F0348H CAN receive FIFO pointer control

register 0

RFPCTR0L RFPCTR0 W – √ √ 0000H

F0349H RFPCTR0H – √

Note When the CAN0EN bit in the PER2 register is 0, the read value is undefined.

When the CAN0EN bit in the PER2 register is 1, the read value is the initial value listed above.

Loading...

Loading...