RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 162

Dec 10, 2015

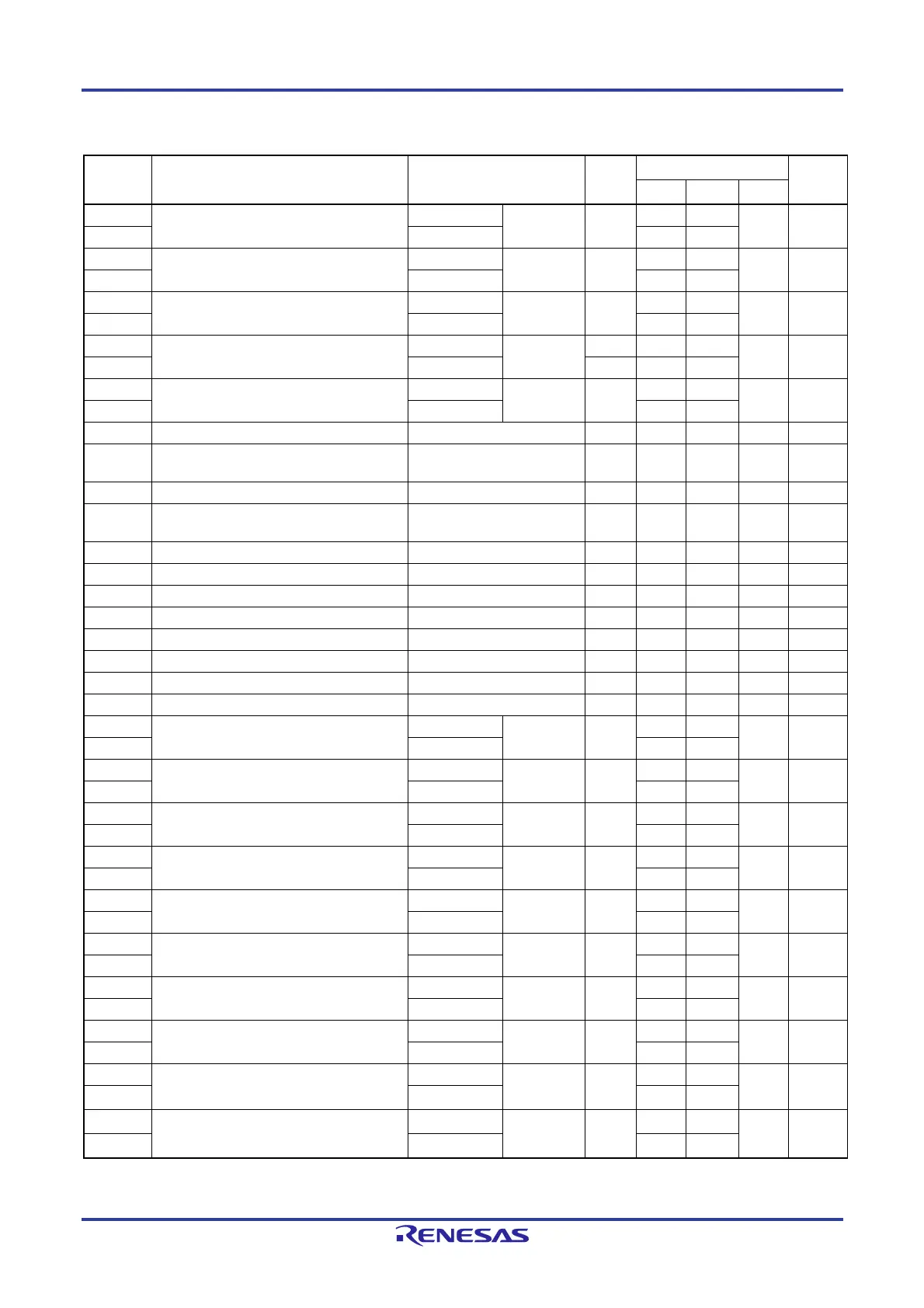

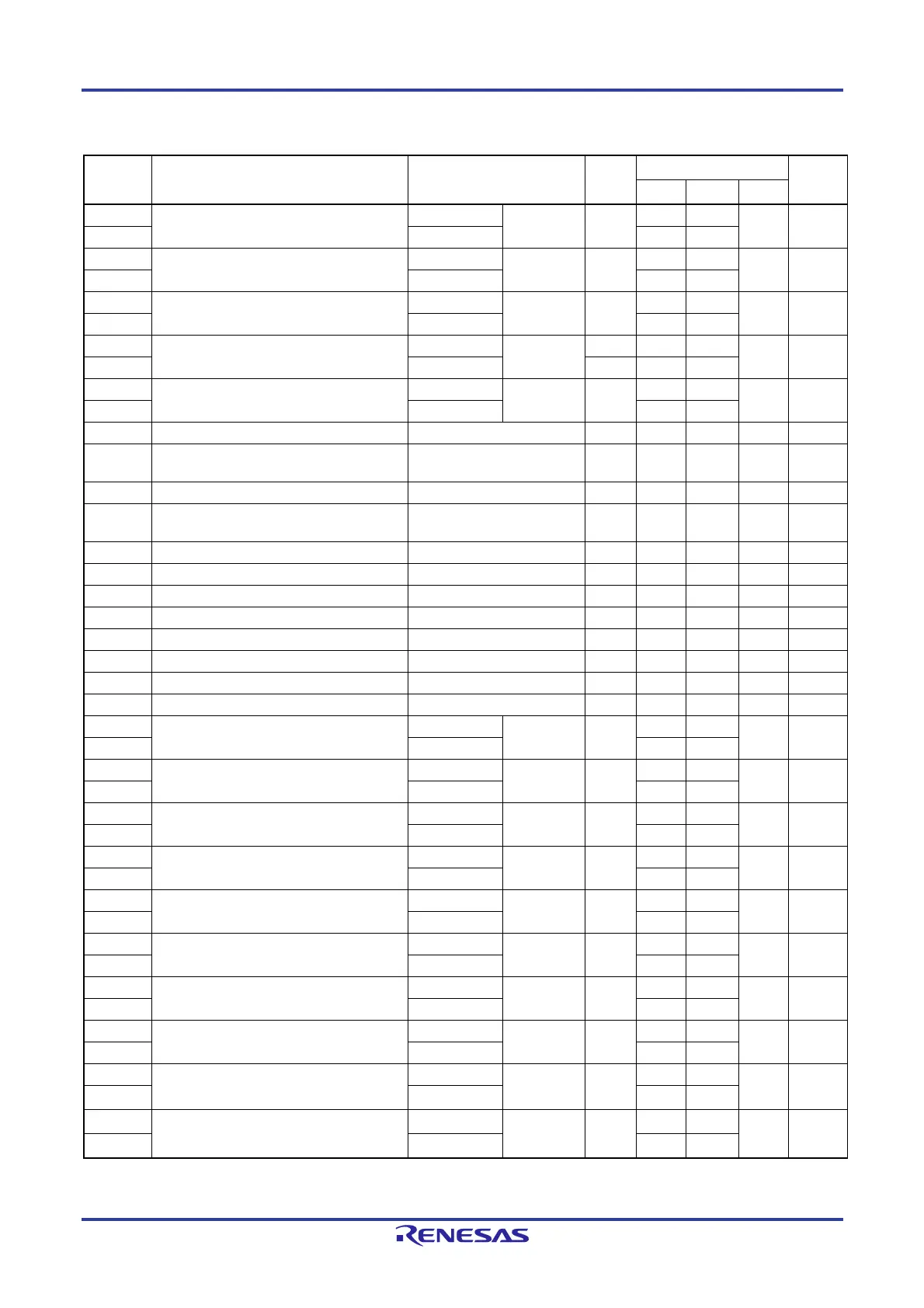

Table 3-6. Extended SFR (2nd SFR) List (11/32)

Address Special Function Register (2nd SFR) Name Symbol R/W Manipulable Bit Range

After

reset

1-bit 8-bit 16-bit

F034AH CAN receive FIFO pointer control register 1 RFPCTR1L RFPCTR1 W – √ √ 0000H

F034BH RFPCTR1H – √

F0350H

CAN0 transmit/receive FIFO control register

0L

CFCCL0L CFCCL0 R/W – √ √ 0000H

F0351H CFCCL0H – √

F0352H

CAN0 transmit/receive FIFO control register

0H

CFCCH0L CFCCH0 R/W – √ √ 0000H

F0353H CFCCH0H – √

F0358H

CAN0 transmit/receive FIFO status register

0

CFSTS0L CFSTS0 R/W – √ √

0001H

Note

F0359H CFSTS0H R – √

F035CH

CAN0 transmit/receive FIFO pointer control

register 0

CFPCTR0L CFPCTR0 W – √ √ 0000H

F035DH – – –

F0360H Receive FIFO message lost status register RFMSTS R – √ – 00H

F0361H

CAN0 transmit//receive FIFO message lost

status register

CFMSTS R – √ – 00H

F0362H CAN receive FIFO interrupt status register RFISTS R – √ – 00H

F0363H

CAN transmit/receive FIFO receive interrupt

status register

CFISTS R – √ – 00H

F0364H CAN0 transmit buffer control register 0 TMC0 R/W – √ – 00H

F0365H CAN0 transmit buffer control register 1 TMC1 R/W – √ – 00H

F0366H CAN0 transmit buffer control register 2 TMC2 R/W – √ – 00H

F0367H CAN0 transmit buffer control register 3 TMC3 R/W – √ – 00H

F036CH CAN0 transmit buffer status register 0 TMSTS0 R/W – √ – 00H

F036DH CAN0 transmit buffer status register 1 TMSTS1 R/W – √ – 00H

F036EH CAN0 transmit buffer status register 2 TMSTS2 R/W – √ – 00H

F036FH CAN0 transmit buffer status register 3 TMSTS3 R/W – √ – 00H

F0374H

CAN0 transmit buffer transmit request

status register

TMTRSTSL TMTRSTS R – √ √ 0000H

F0375H TMTRSTSH – √

F0376H

CAN0 transmit buffer transmit complete

status register

TMTCSTSL TMTCSTS R – √ √ 0000H

F0377H TMTCSTSH – √

F0378H

CAN0 transmit buffer transmit abort status

register

TMTASTSL TMTASTS R – √ √ 0000H

F0379H TMTASTSH – √

F037AH

CAN0 transmit buffer interrupt enable

register

TMIECL TMIEC R/W – √ √ 0000H

F037BH TMIECH – √

F037CH CAN0 transmit history buffer control register THLCC0L THLCC0 R/W – √ √ 0000H

F037DH THLCC0H – √

F0380H CAN0 transmit history buffer status register THLSTS0L THLSTS0 R/W – √ √

0001H

Note

F0381H THLSTS0H – √

F0384H

CAN0 transmit history buffer pointer control

register

THLPCTR0L THLPCTR0 W – √ √ 0000H

F0385H THLPCTR0H – √

F0388H CAN global transmit interrupt status register GTINTSTSL GTINTSTS R – √ √ 0000H

F0389H GTINTSTSH – √

F038AH CAN global RAM window control register GRWCRL GRWCR R/W – √ √ 0000H

F038BH GRWCRH –

√

F038CH CAN global test configuration register GTSTCFGL GTSTCFG R/W –

√ √

0000H

F038DH GTSTCFGH –

√

Note When the CAN0EN bit in the PER2 register is 0, the read value is undefined.

When the CAN0EN bit in the PER2 register is 1, the read value is the initial value listed above.

Loading...

Loading...