Rockwell Automation Publication 2080-UM002M-EN-E - April 2022 197

Chapter 9 Use the High-Speed Counter and Programmable Limit Switch

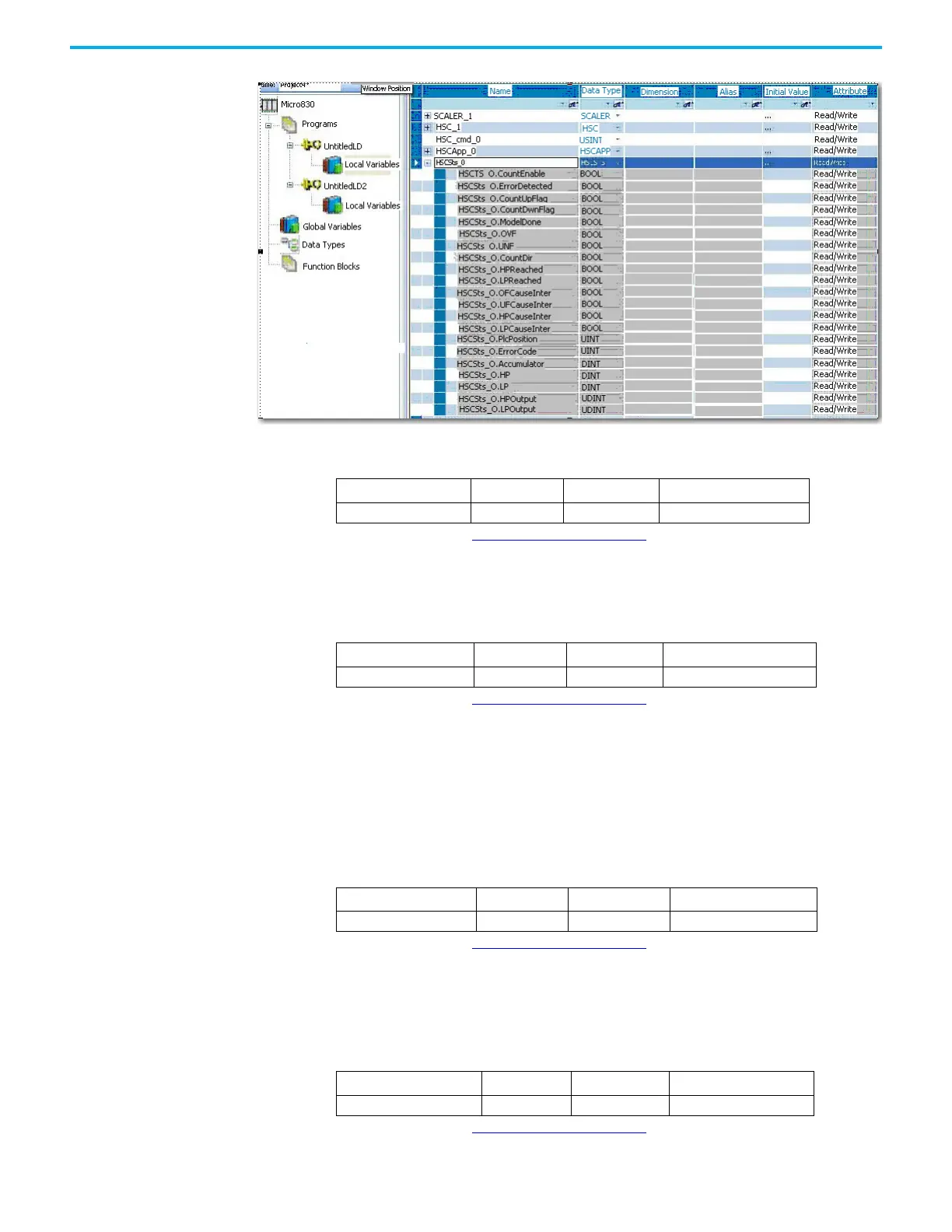

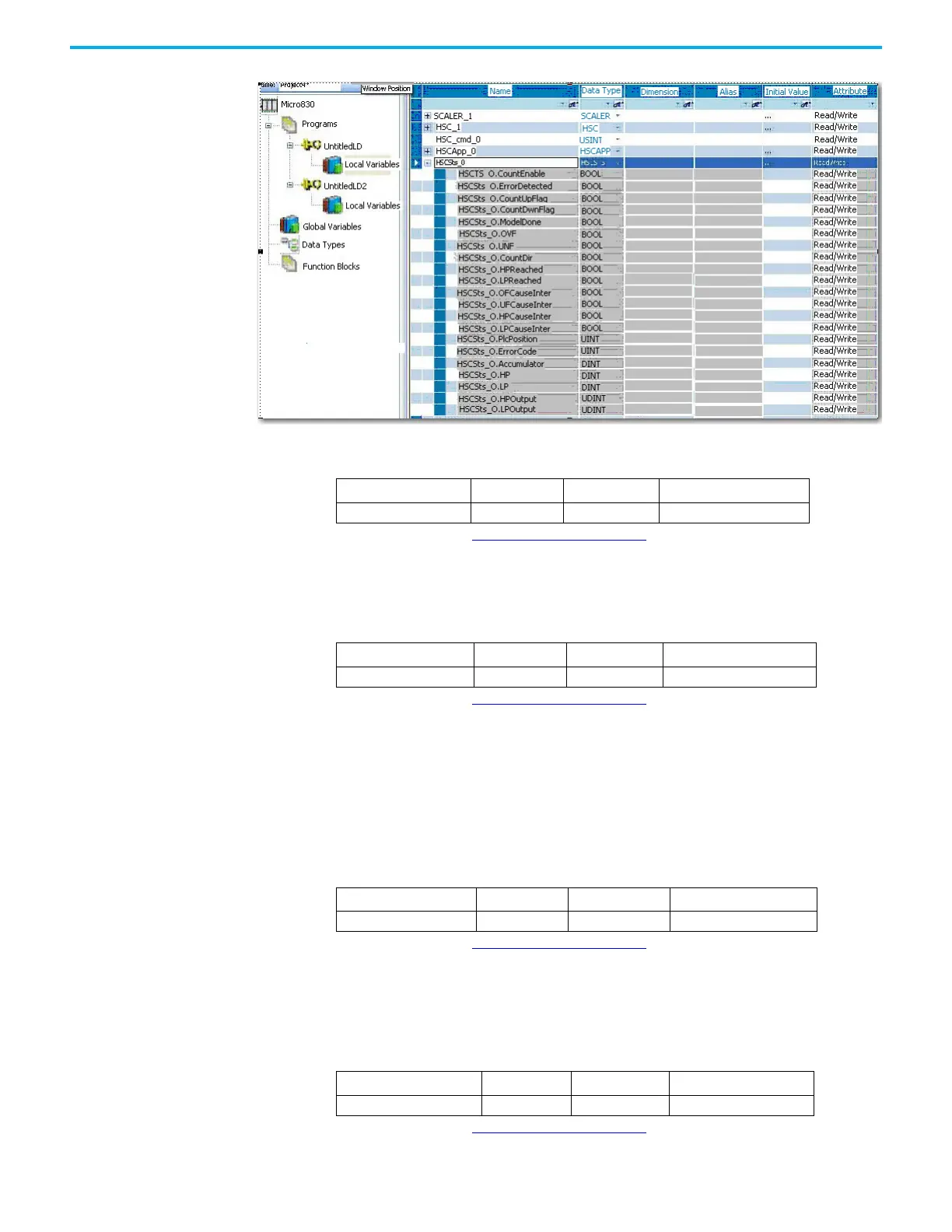

The Counting Enabled control bit is used to indicate the status of the High-

Speed Counter, whether counting is enabled (1) or disabled (0, default).

The Error Detected flag is a status bit that can be used in the control program

to detect if an error is present in the HSC sub-system. The most common type

of error that this bit represents is a configuration error. When this bit is set (1),

you should look at the specific error code in parameter HSCSTS.ErrorCode.

This bit is maintained by the controller and is set when there is an HSC error.

This bit can be cleared by the user, if necessary.

The Count Up bit is used with all of the HSCs (modes 0…9). If the

HSCSTS.CountEnable bit is set, the Count Up bit is set (1). If the

HSCSTS.CountEnable is cleared, the Count Up bit is cleared (0).

Counting Enabled (HSCSTS.CountEnable)

Description Data Format

HSC Modes

(1)

(1) For Mode descriptions, see HSC Mode (HSCAPP.HSCMode) on page 189.

User Program Access

HSCSTS.CountEnable bit 0…9 read only

Error Detected (HSCSTS.ErrorDetected)

Description Data Format

HSC Modes

(1)

(1) For Mode descriptions, see HSC Mode (HSCAPP.HSCMode) on page 189.

User Program Access

HSCSTS.ErrorDetected bit 0…9 read/write

Count Up (HSCSTS.CountUpFlag)

Description Data Format

HSC Modes

(1)

(1) For Mode descriptions, see HSC Mode (HSCAPP.HSCMode) on page 189.

User Program Access

HSCSTS.CountUpFlag bit 0…9 read only

Count Down (HSCSTS.CountDownFlag)

Description Data Format

HSC Modes

(1)

(1) For Mode descriptions, see HSC Mode (HSCAPP.HSCMode) on page 189.

User Program Access

SCSTS.CountDownFlag bit 2…9 read only

Loading...

Loading...