SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 102 Version 1.5

SLAVE modea STOP condition was received.

NACK done status.

0 : Not received a NACK.

1 : Received a NACK.

ACK done status.

0 : Not received an ACK.

1 : Received an ACK.

RX done status.

0: No RX with ACK/NACK transfer.

1: 8-bit RX with ACK/NACK transfer is done.

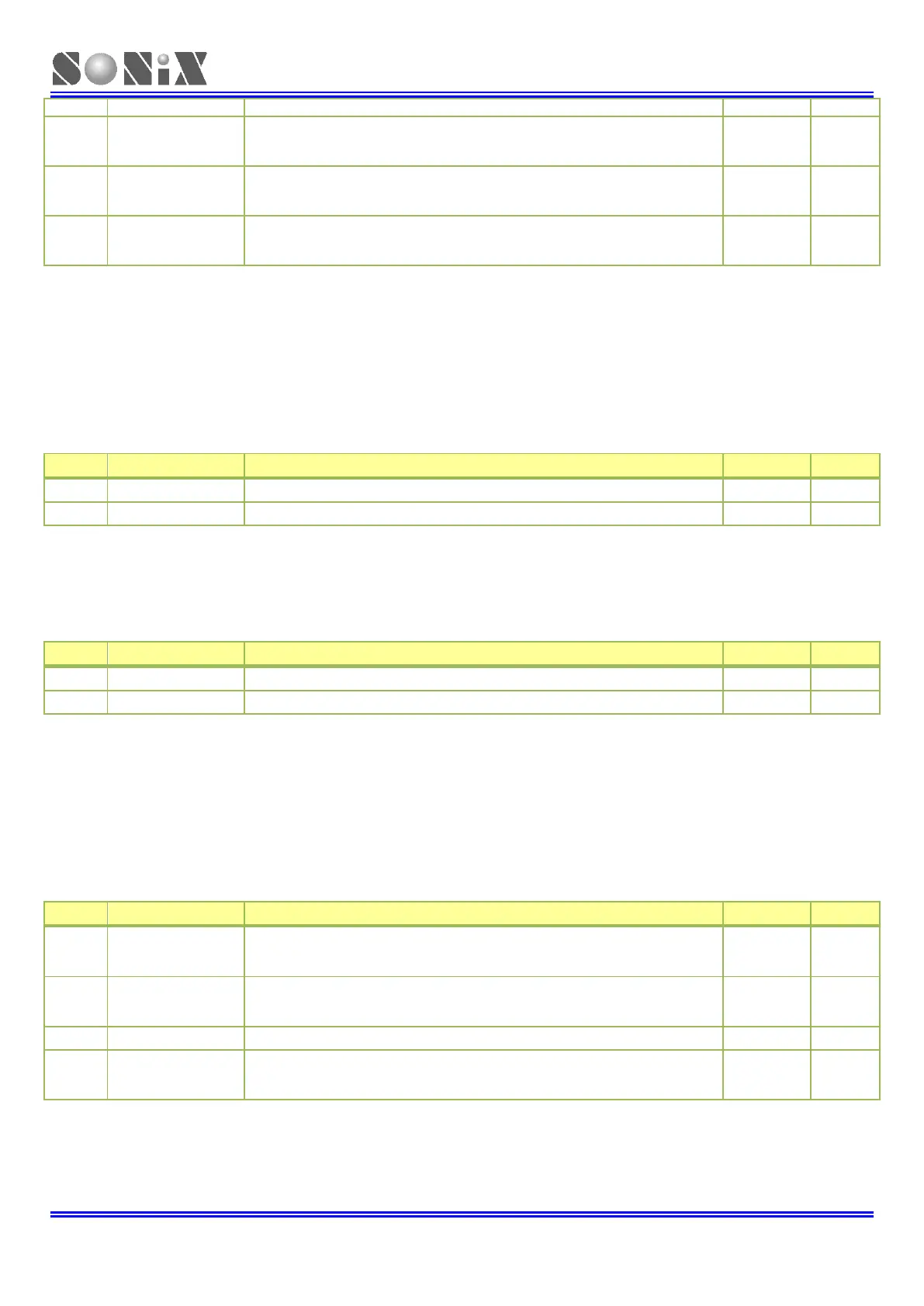

9.7.3 I2C n TX Data register (I2Cn_TXDATA) (n=0)

Address Offset: 0x08

This register contains the data to be transmitted.

In Master TX mode, CPU writes this register will trigger a TX function. In Slave TX mode, CPU has to write this register

before next TX procedure.

9.7.4 I2C n RX Data register (I2Cn_RXDATA) (n=0)

Address Offset: 0x0C

Contains the data received. Read this register when RX_DN = 1.

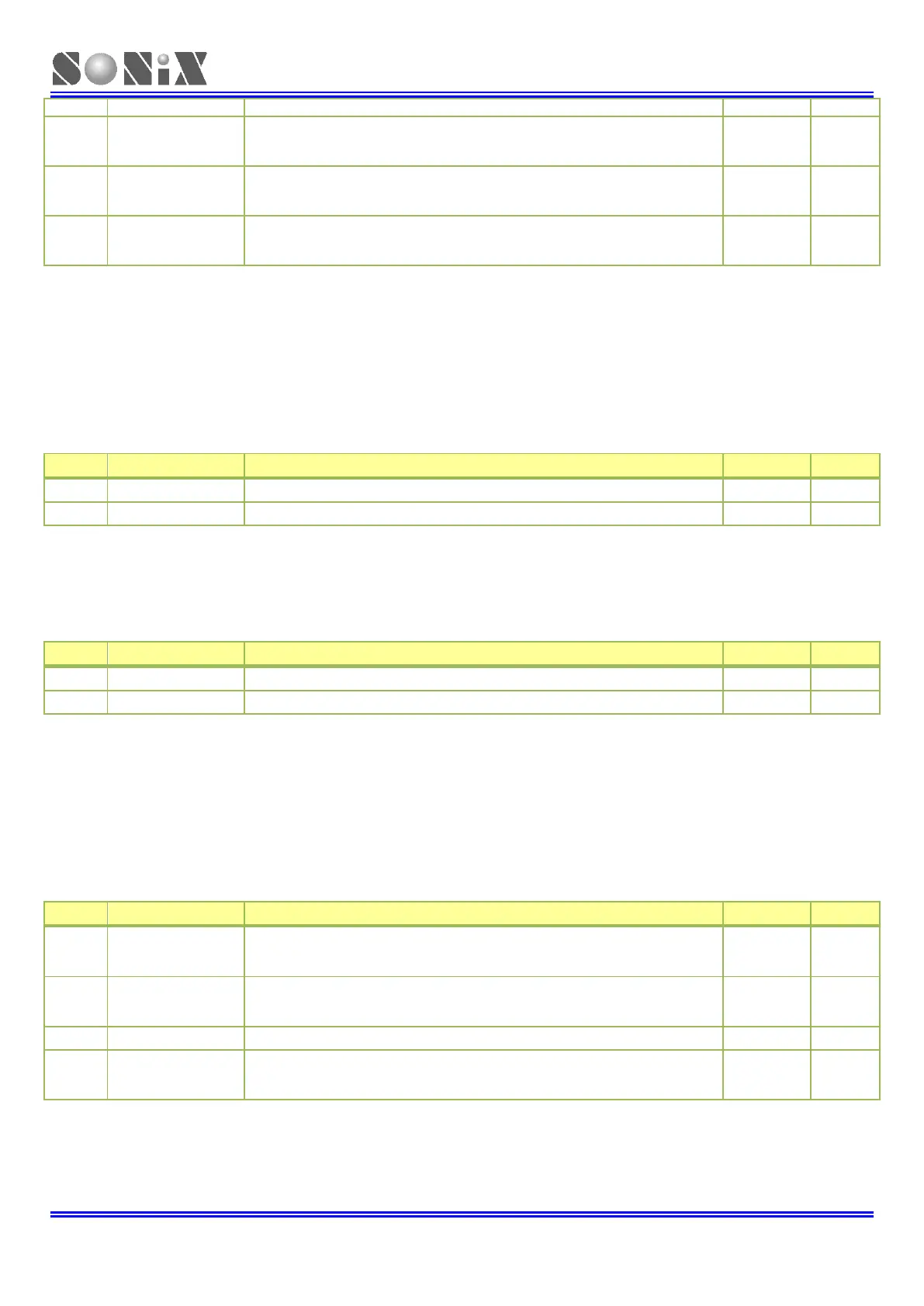

9.7.5 I2C n Slave Address 0 register (I2Cn_SLVADDR0) (n=0)

Address Offset: 0x10

Only used in slave mode. In master mode, this register has no effect.

If this register contains 0x00, the I2C will not acknowledge any address on the bus. Register ADR0 to ADR3 will be

cleared to this disabled state on reset.

Slave address mode.

0 : 7-bit address mode.

1: 10-bit address mode.

General call address enable bit..

0: Disable.

1: Enable general call address. (0x0)

The I2C slave address.

ADD[9:0] is valid when ADD_MODE = 1.

ADD[7:1] is valid when ADD_MODE = 0.

9.7.6 I2C n Slave Address 1~3 register (I2Cn_SLVADDR1~3) (n=0)

Address Offset: 0x14, 0x18, 0x1C

Loading...

Loading...