SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 44 Version 1.5

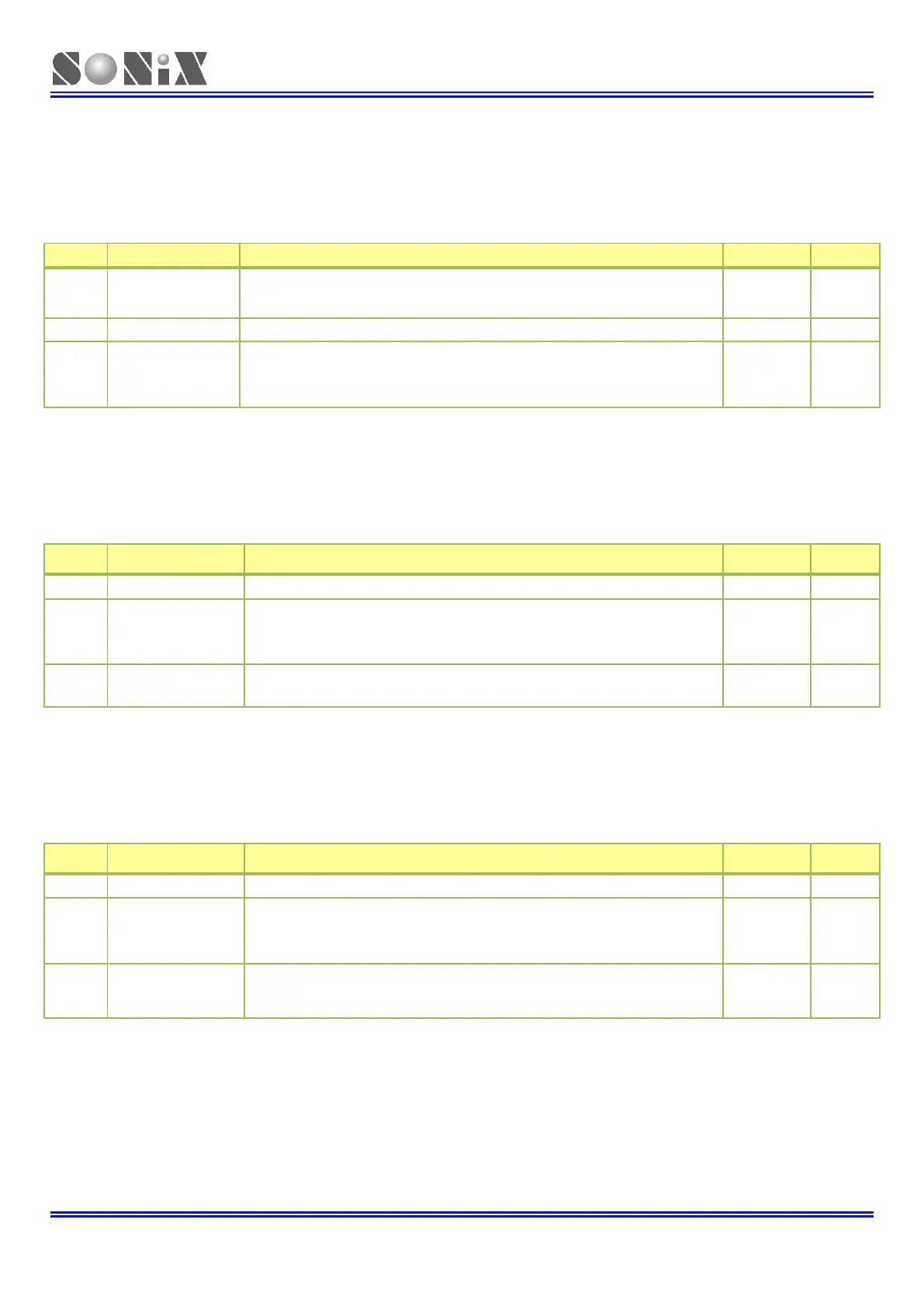

3.3.9 Interrupt Vector Table Mapping register (SYS0_IVTM)

Address Offset: 0x24

This register decides whether the ARM interrupt vector table is mapping to User ROM or SRAM.

IVTM register key.

Read as 0. Behaviour of writing to this register is ignored unless writing

0xA5A5 to IVTMKEY at the same time.

Interrupt table mapping selection.

01: Map to User ROM.

10: Map to SRAM.

00,11: Reserved.

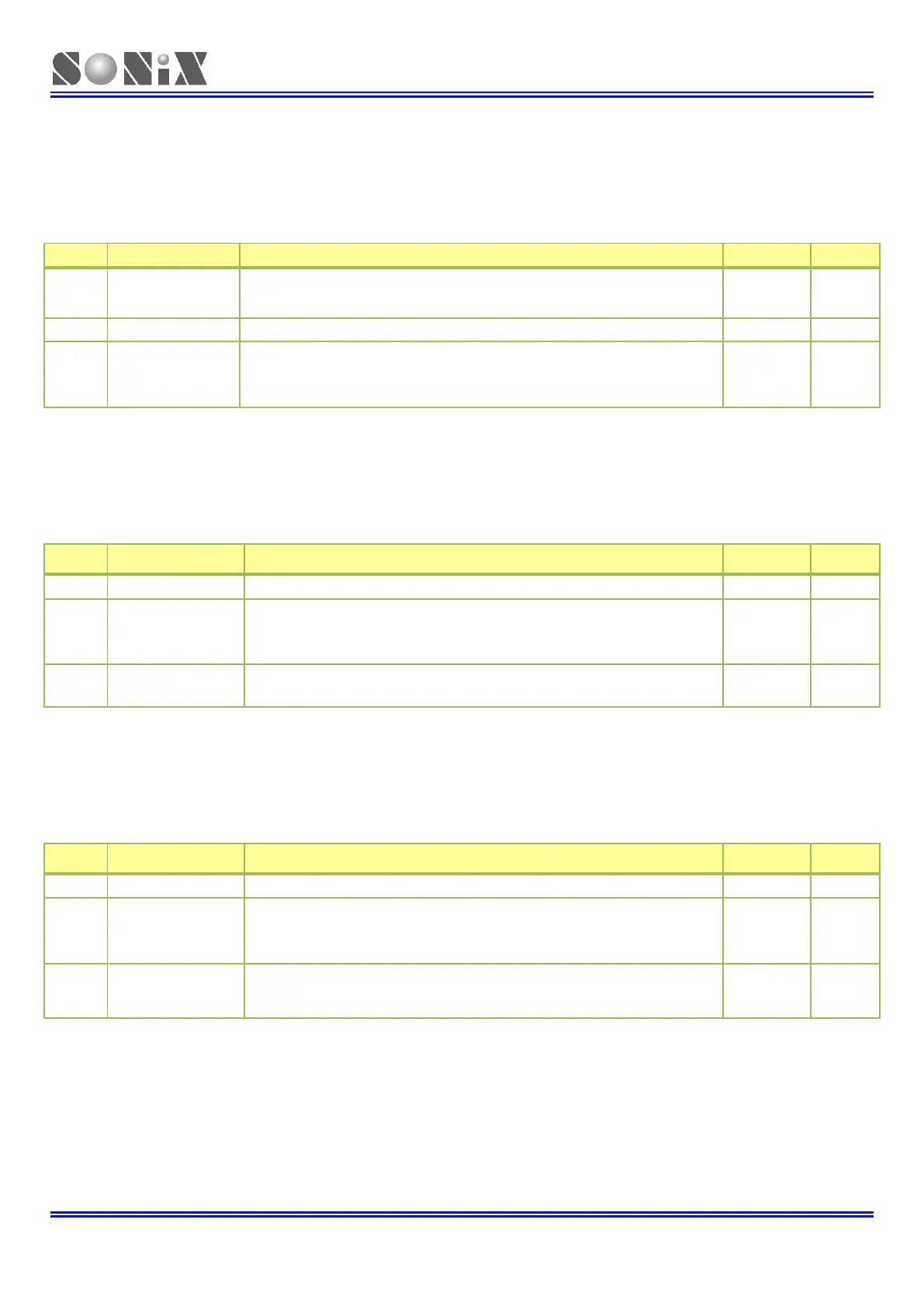

3.3.10 Noise Detect Control register (SYS0_NDTCTRL)

Address Offset: 0x28

NDT0: Disablefor VDD 5V interrupt enable bit.

0: Disable.

1: Enable. (The noise on IC VDD 5V domain detected by NDT5V IP will

trigger.NDT interrupt IRQ0)

3.3.11 Noise Detect Status register (SYS0_NDTSTS)

Address Offset: 0x2C

Power noise status of NDT5V IP.

0: No power noise is detected.

1: Power noise is detected by NDT5V IP.

*Cleared by write 1 to SYS0_NDTSTS[1]

3.3.12 Anti-EFT Ability Control register (SYS0_ANTIEFT)

Address Offset: 0x30

This register decides the HW anti-EFT ability.

Loading...

Loading...