SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 41 Version 1.5

3.3 SYSTEM CONTROL REGISTERS 0

Base Address: 0x4006 0000

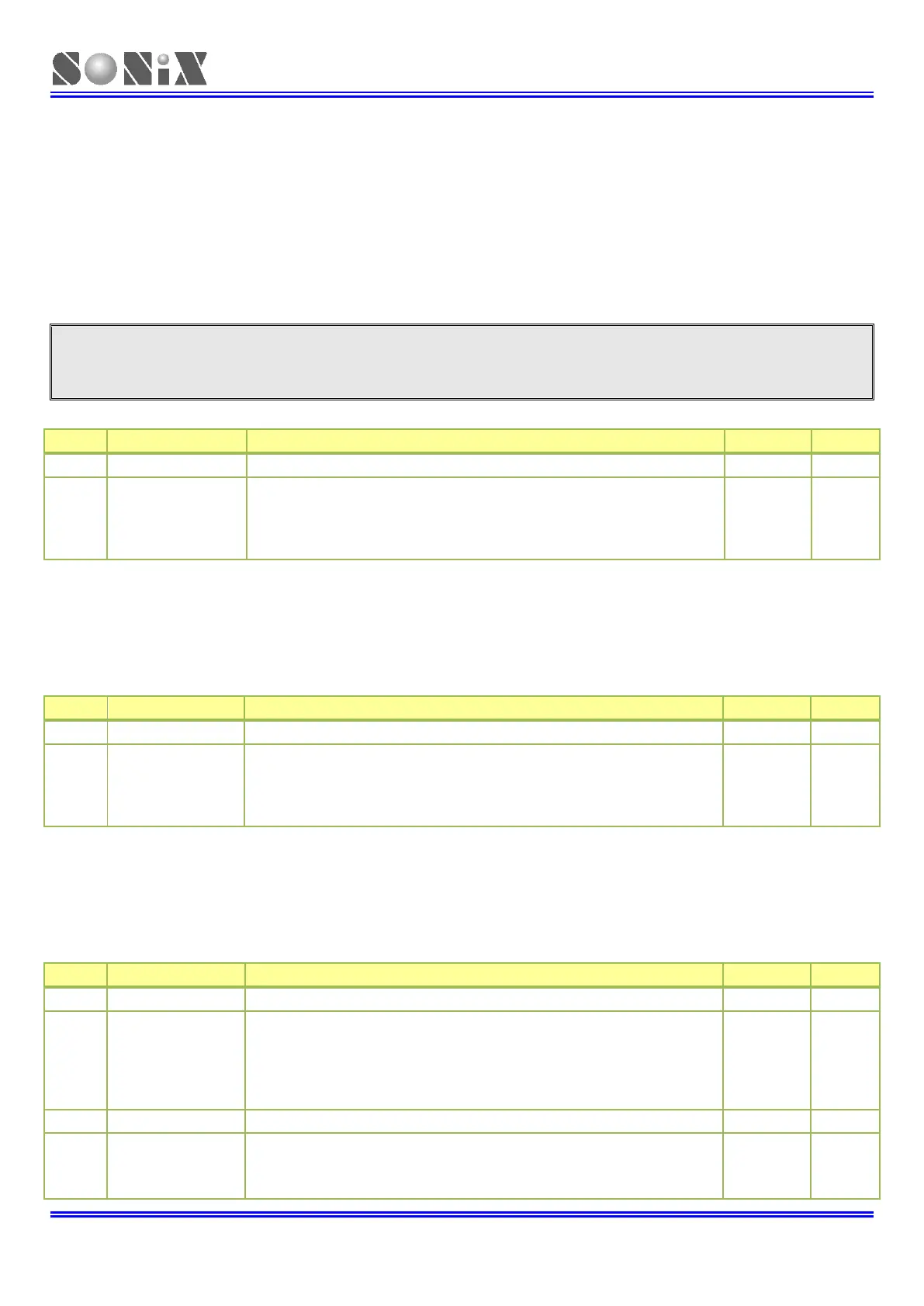

3.3.1 Analog Block Control register (SYS0_ANBCTRL)

Address Offset: 0x00

Reset value: 0x0000 0001

Note: IHRCEN bit can NOT be cleared if the IHRC is selected as system clock or is selected to become

the system clock.

Internal high-speed clock enable.

Note: This bit can NOT be cleared if the IHRC is selected as system clock

or is selected to become the system clock.

0: Disable internal 48 MHz RC oscillator.

1: Enable internal 48 MHz RC oscillator.

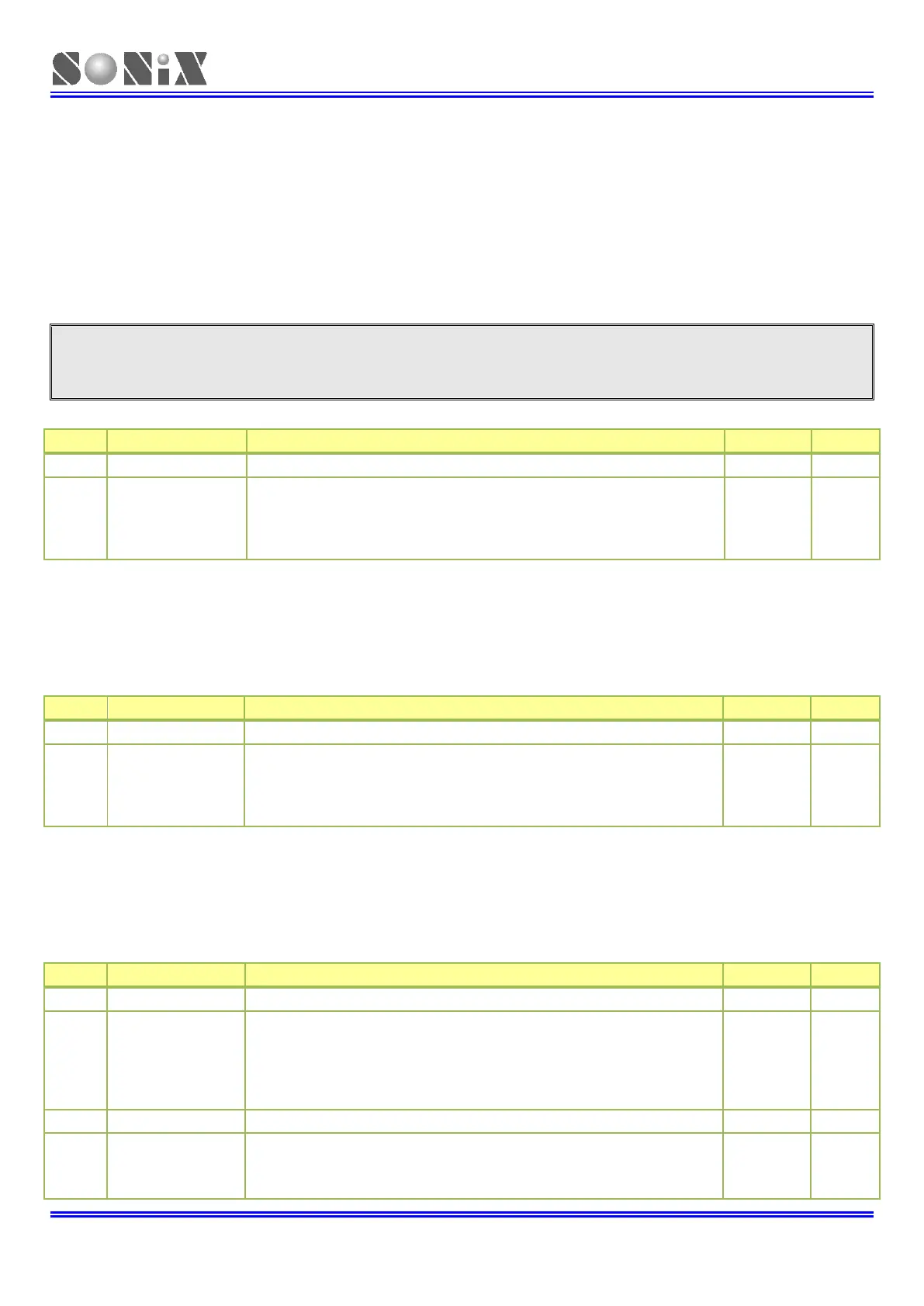

3.3.2 Clock Source Status register (SYS0_CSST)

Address Offset: 0x08

IHRC ready flag.

After the IHRCEN bit is cleared, IHRCRDY is cleared by HW after 6 IHRC

clock cycles.

0: IHRC not ready.

1: IHRC ready.

3.3.3 System Clock Configuration register (SYS0_CLKCFG)

Address Offset: 0x0C

System clock switch status

Set and cleared by HW to indicate which clock source is used as system

clock.

000: IHRC is used as system clock

001: ILRC is used as system clock

Other: Reserved

System clock switch

Set and cleared by SW.

000: IHRC

001: ILRC

Loading...

Loading...