SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 93 Version 1.5

1: Enable and HW switches I/O configurations refer to FORMAT bit

directly.

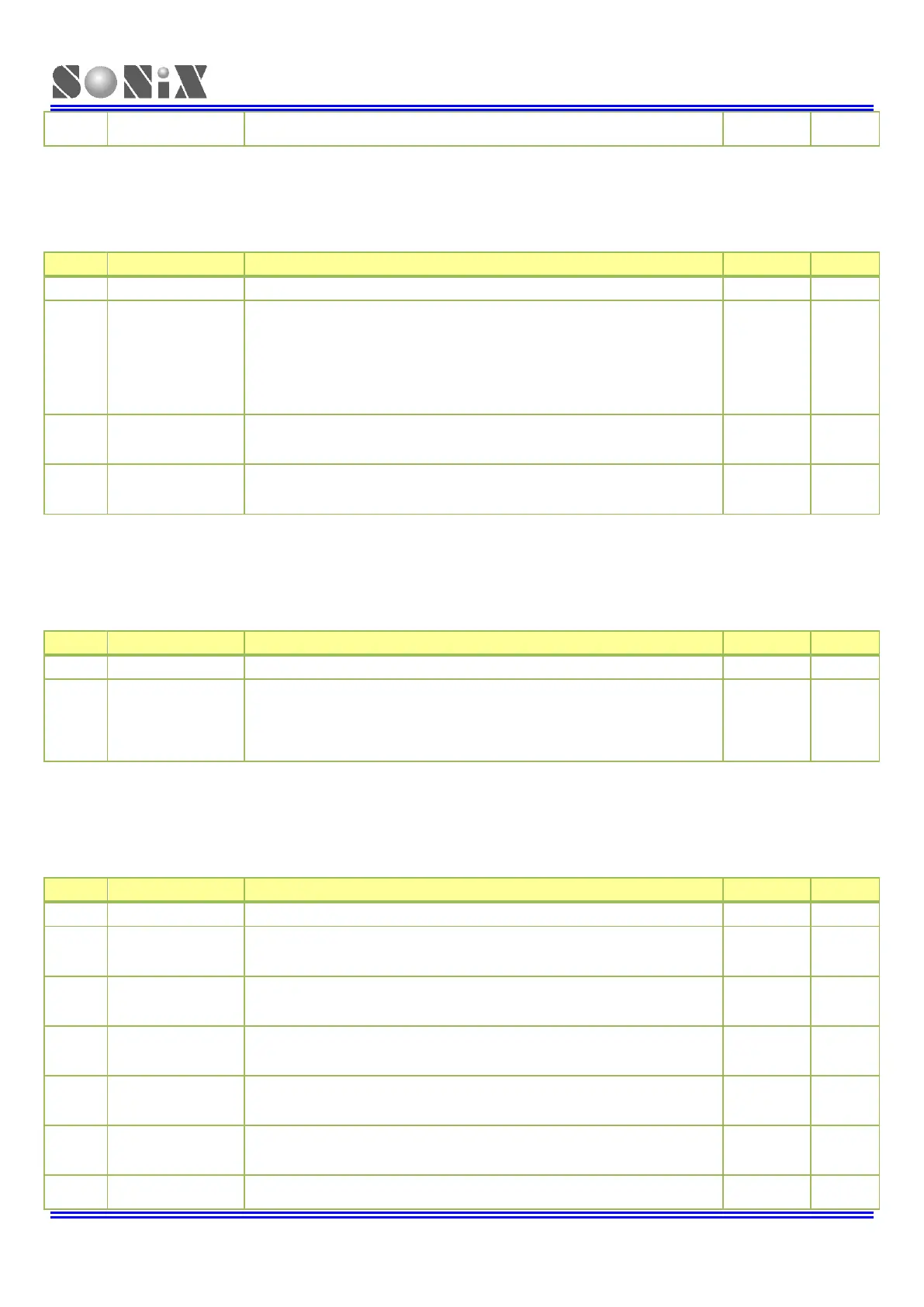

8.6.2 SPI n Control register 1 (SPIn_CTRL1) (n=0)

Address Offset: 0x04

Clock phase for edge sampling.

0: Data changes at clock falling edge, latches at clock rising edge when

CPOL = 0; Data changes at clock rising edge, latches at clock falling

edge when CPOL = 1.

1: Data changes at clock rising edge, latches at clock falling edge when

CPOL = 0; Data changes at clock falling edge, latches at clock rising

edge when CPOL = 1.

Clock polarity selection bit.

0: SCK idles at Low level.

1: SCK idles at High level.

MSB/LSB selection bit

0: MSB transmit first.

1: LSB transmit first.

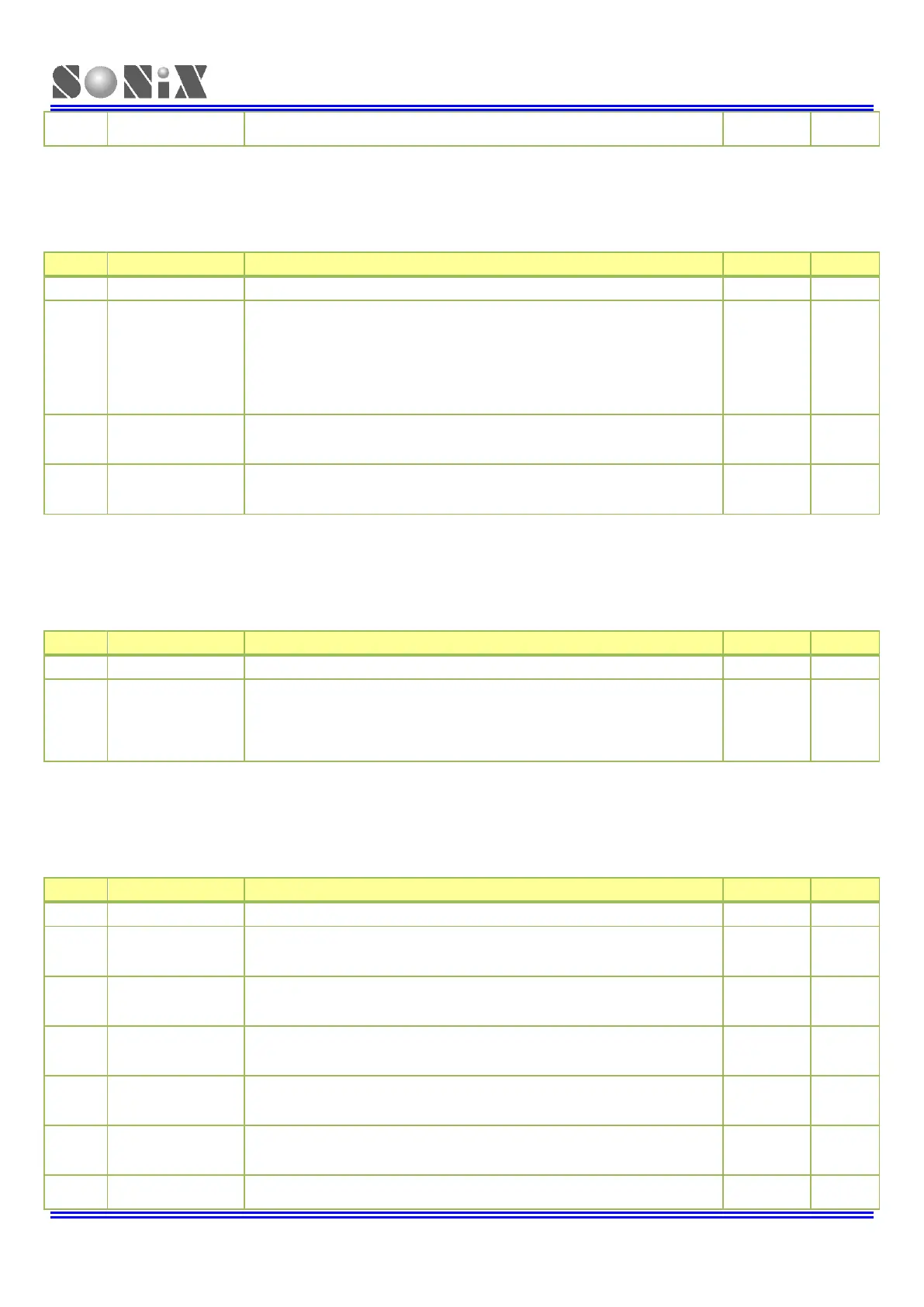

8.6.3 SPI n Clock Divider register (SPIn _CLKDIV) (n=0)

Address Offset: 0x08

SPIn clock divider

0: SCK = SSPn_PCLK / 2

1: SCK = SSPn_PCLK / 4

2: SCK = SSPn_PCLK / 6

X: SCK = SSPn_PCLK / (2X+2)

8.6.4 SPI n Status register (SPIn _STAT) (n=0)

Address Offset: 0x0C

RX FIFO threshold flag.

0: Data in RX FIFO ≤ RXFIFOTH.

1: Data in RX FIFO > RXFIFOTH.

TX FIFO threshold flag.

0: Data in TX FIFO > TXFIFOTH.

1: Data in TX FIFO ≤ TXFIFOTH.

Busy flag.

0: SPI controller is idle.

1: SPI controller is transferring.

RX FIFO full flag.

0: RX FIFO is NOT full.

1: RX FIFO is full.

RX FIFO empty flag.

0: RX FIFO is NOT empty.

1: RX FIFO is empty.

TX FIFO full flag.

0: TX FIFO is NOT full.

Loading...

Loading...