SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 124 Version 1.5

SERIAL-WIRE DEBUG (SWD)

12.1 OVERVIEW

SWD functions are integrated into the ARM Cortex-M0. The ARM Cortex-M0 is configured to support up to four

breakpoints and two watch points.

12.2 FEATURES

Supports ARM Serial Wire Debug (SWD) mode.

Direct debug access to all memories, registers, and peripherals.

No target resources are required for the debugging session.

Up to four breakpoints.

Up to two data watch points that can also be used as triggers.

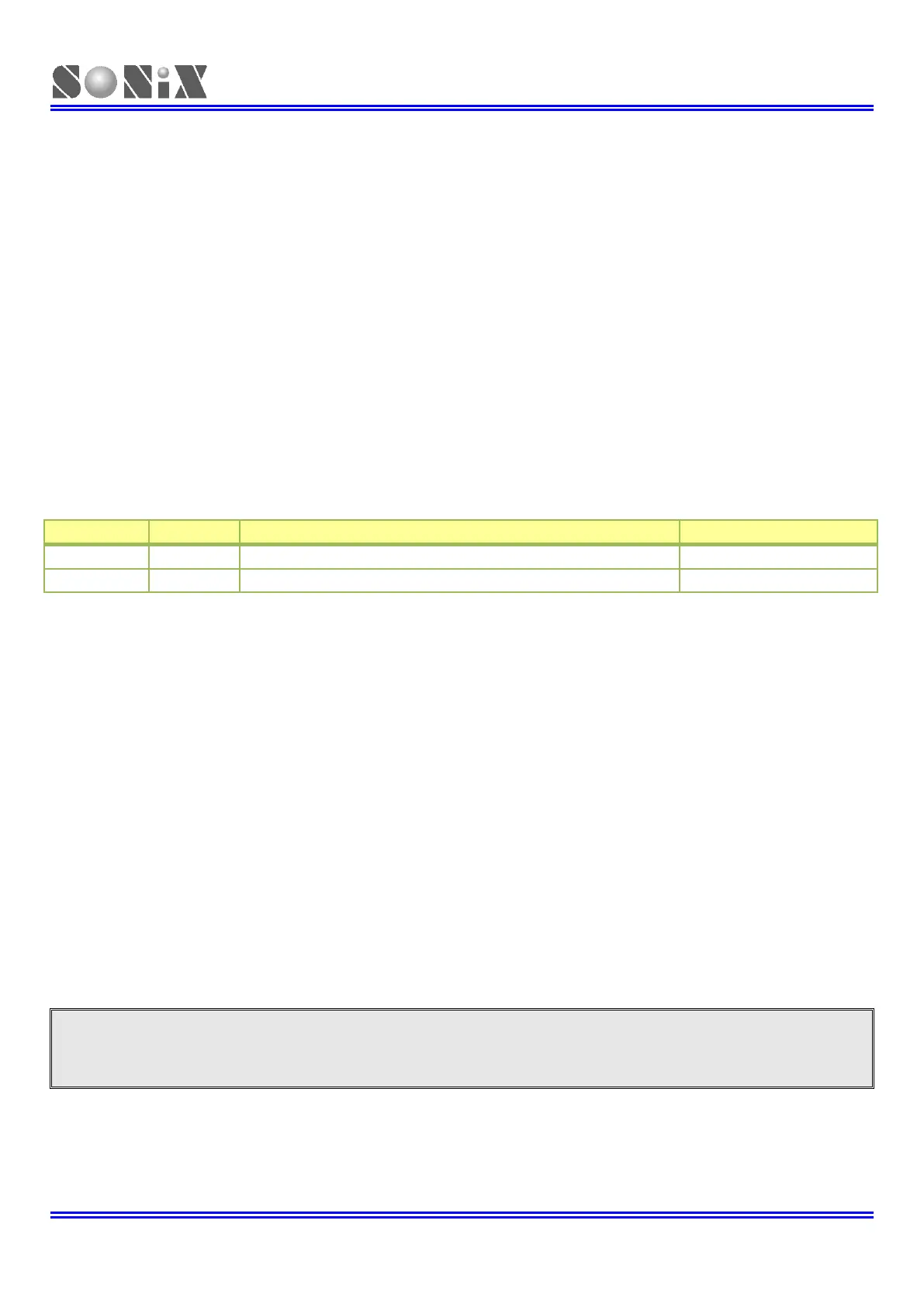

12.3 PIN DESCRIPTION

Serial Wire Clock pin in SWD mode.

Serial Wire Data Input/Output pin in SWD mode.

12.4 DEBUG NOTE

12.4.1 LIMITATIONS

Debug mode changes the way in which reduced power modes work internal to the ARM Cortex-M0 CPU, and this

ripples through the entire system. These differences mean that power measurements should not be made while

debugging, the results will be higher than during normal operation in an application.

During a debugging session, the SysTick Timer is automatically stopped whenever the CPU is stopped. Other

peripherals are not affected.

12.4.2 DEBUG RECOVERY

User code may disable SWD function in order to use P3.6 and P3.7 as GPIO, and may not debug by SWD function to

debug or download FW any more.

SONiX provide Boot loader to check the status of P3.5 (BOOT pin) during boot procedure. If P3.5 is Low during Boot

procedure, MCU will execute code in Boot loader instead of User code, so SWD function is not disabled.

Exit Boot loader, user code can still configure P3.5 as other functions such as GPIO.

Note: We strongly recommanded NOT using BOOT pin as output pin to drive the LED, otherwise, the

BOOT pin status may be low during boot procedure.

Loading...

Loading...