SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 46 Version 1.5

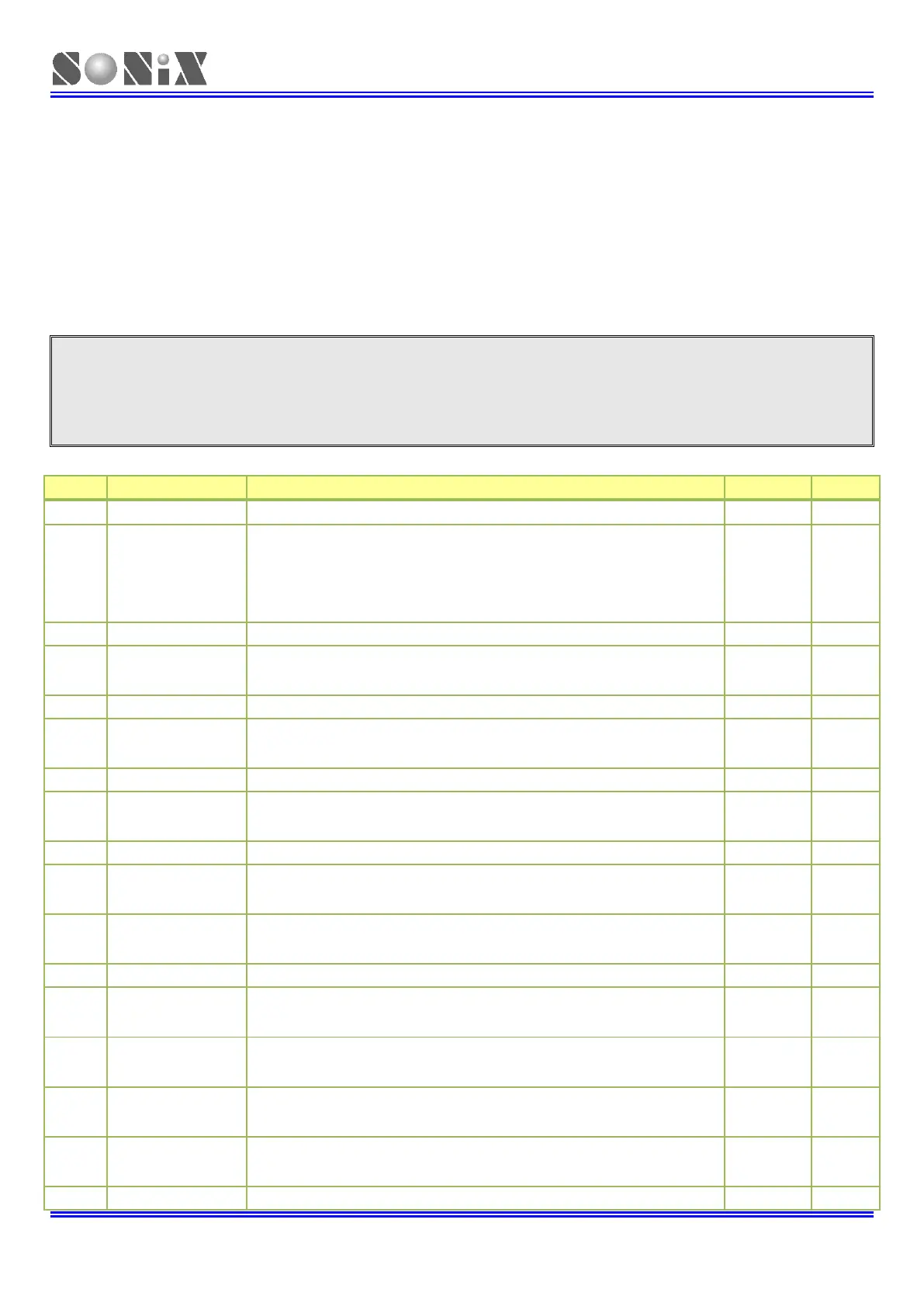

3.4 SYSTEM CONTROL REGISTERS 1

Base Address: 0x4005 E000

3.4.1 AHB Clock Enable register (SYS1_AHBCLKEN)

Address Offset: 0x00

The SYS_AHBCLKEN register enables the AHB clock to individual system and peripheral blocks.

Note:

1. When the clock is disabled, the peripheral register values may not be readable by SW and the

value returned is always 0x0.

2. HW will replace GPIO with CLKOUT function directly if CLKOUTSEL is Not 0.

Clock output source

000: Disable

001: ILRC clock

100: HCLK

101: IHRC clock

Others: Reserved.

Enables clock for WDT.

0: Disable

1: Enable

Enables clock for I2C0.

0: Disable

1: Enable

Enables clock for SPI0.

0: Disable

1: Enable

Enables clock for CT16B1.

0: Disable

1: Enable

Enables clock for CT16B0.

0: Disable

1: Enable

Enable clock for USB

0: Disable

1: Enable

Enables clock for P3.

0: Disable

1: Enable

Enables clock for P2.

0: Disable

1: Enable

Enables clock for P1.

0: Disable

1: Enable

Loading...

Loading...