SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 94 Version 1.5

TX FIFO empty flag.

0: TX FIFO is NOT empty. In Master mode, the transmitter will begin to

transmit automatically.

1: TX FIFO is empty.

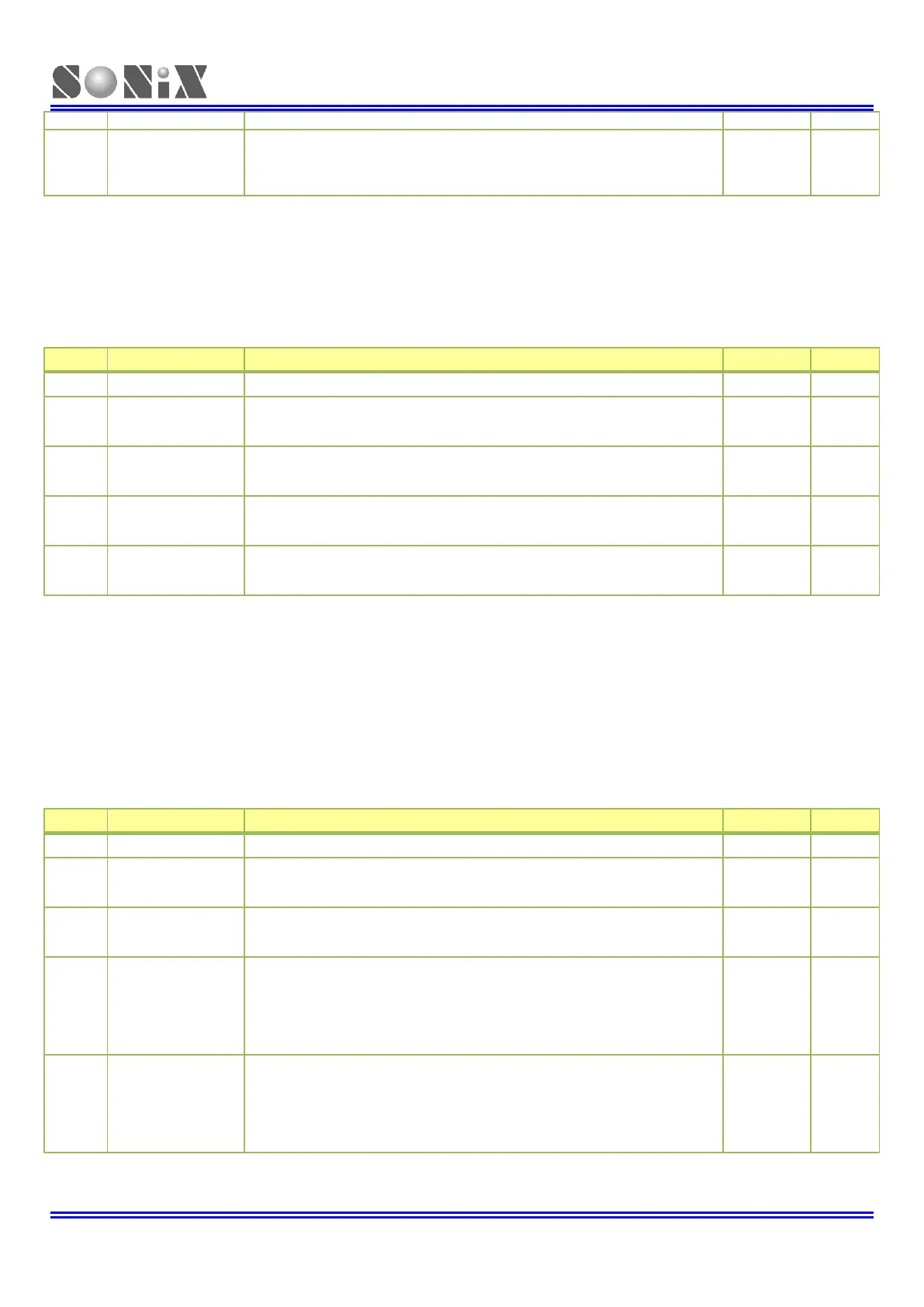

8.6.5 SPI n Interrupt Enable register (SPIn _IE) (n=0)

Address Offset: 0x10

This register controls whether each of the four possible interrupt conditions in the SPI controller is enabled.

TX FIFO threshold interrupt enable.

0: Disable.

1: Enable.

RX FIFO threshold interrupt enable.

0: Disable.

1: Enable.

RX time-out interrupt enable.

0: Disable.

1: Enable.

RX Overflow interrupt enable.

0: Disable.

1: Enable.

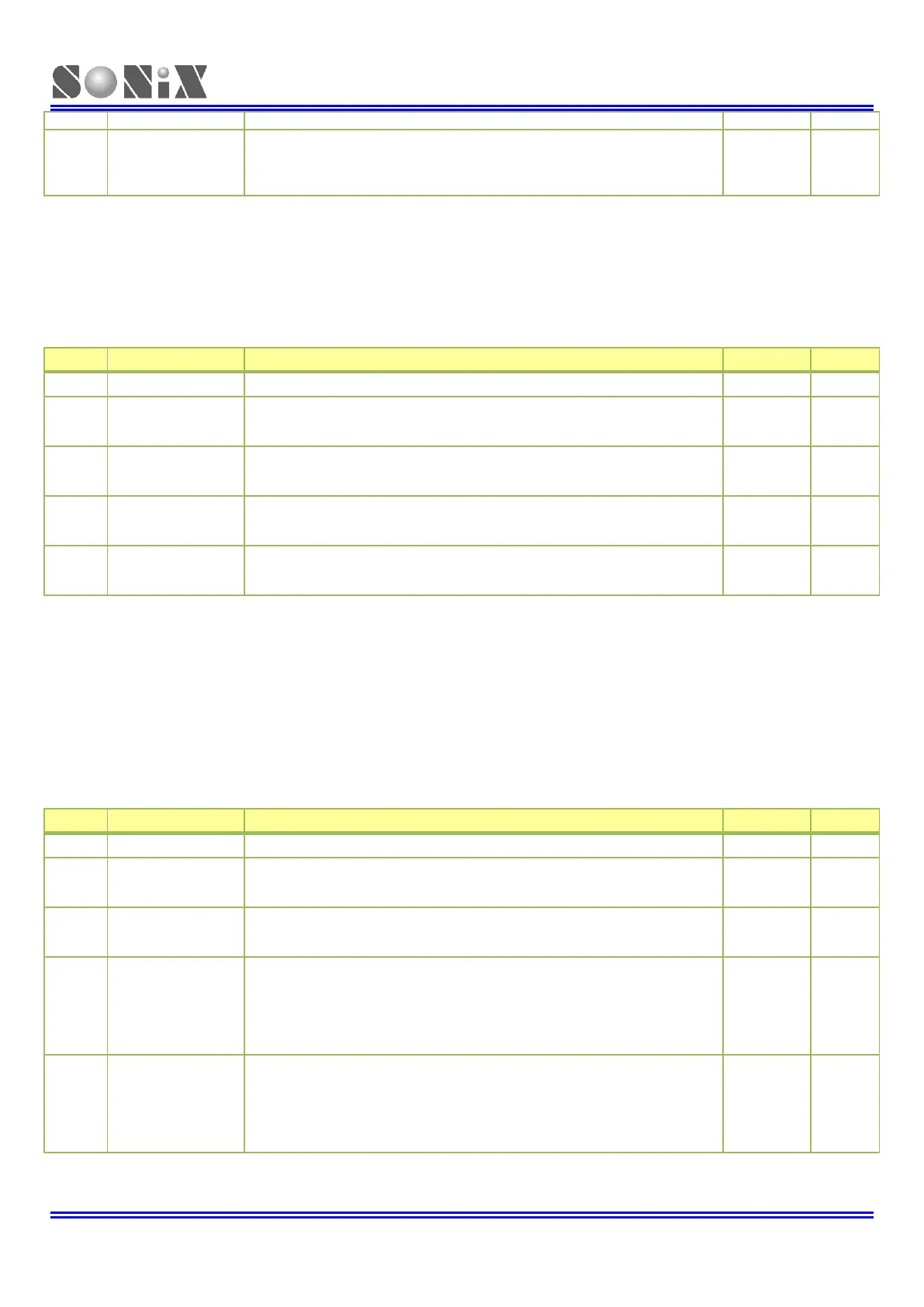

8.6.6 SPI n Raw Interrupt Status register (SPIn _RIS) (n=0)

Address Offset: 0x14

This register contains the status for each interrupt condition, regardless of whether or not the interrupt is enabled in

SPIn_IE register.

This register indicates the status for SPI control raw interrupts. An SPI interrupt is sent to the interrupt controller if the

corresponding bit in the SPIn_IE register is set.

TX FIFO threshold interrupt flag.

0: No TX FIFO threshold interrupt.

1: TX FIFO threshold triggered.

RX FIFO threshold interrupt flag.

0: No RX FIFO threshold interrupt.

1: RX FIFO threshold triggered.

RX time-out interrupt flag.

RXTO occurs when the RX FIFO is not empty, and has not been read for a

time-out period (32*SSPn_PCLK). The time-out period is the same for

master and slave modes.

0: RXTO doesn’t occur.

1: RXTO occurs.

RX Overflow interrupt flag.

RXOVF occurs when the RX FIFO is full and another frame is completely

received. The ARM spec implies that the preceding frame data is

overwritten by the new frame data when this occurs.

0: RXOVF doesn’t occur.

1: RXOVF occurs.

Loading...

Loading...