SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 122 Version 1.5

11.11 FMC REGISTERS

Base Address: 0x4006 2000

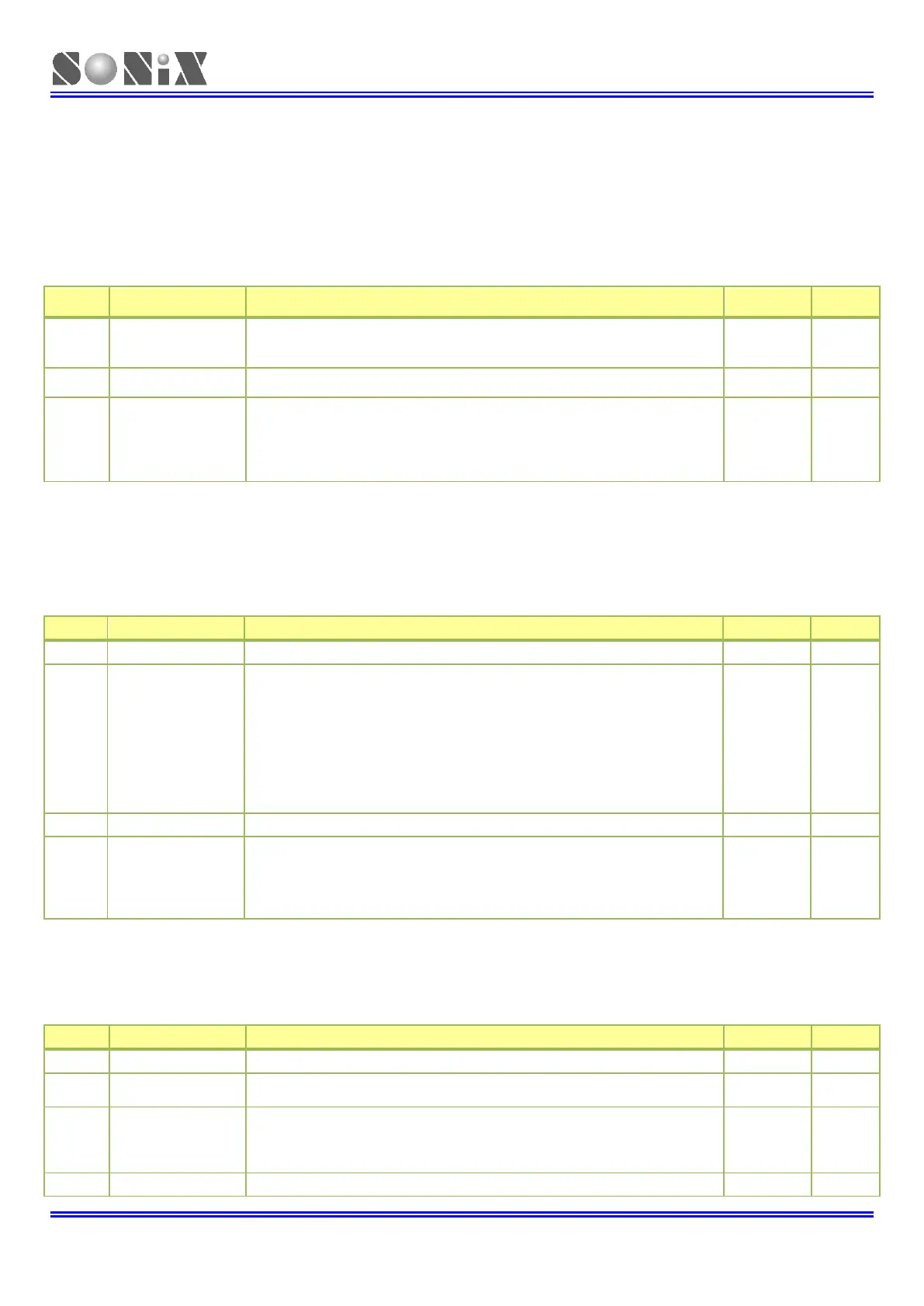

11.11.1 Flash Low Power Control register (FLASH_LPCTRL)

Address offset: 0x00

FMC verify key.

Read as 0. When writing to the register you must write 0x5AFA to

FMCKEY, otherwise behavior of writing to the register is ignored.

Flash Low Power mode selection bit.

0000b: HCLK< 24MHz.

0101b: HCLK≧24MHz.

Other: Reserved, and may cause unexpected error to force MCU enter

Hardfault handler.

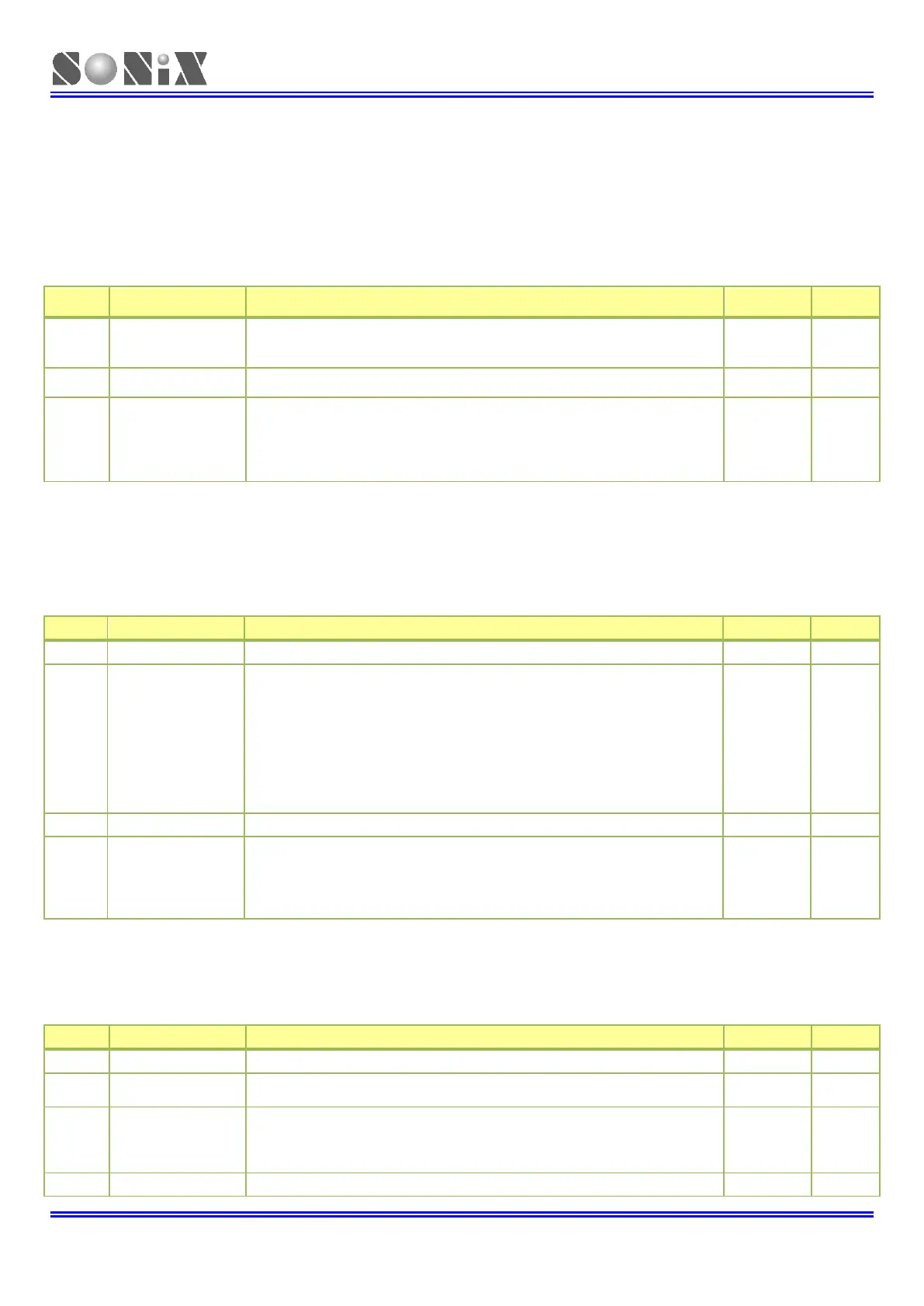

11.11.2 Flash Status register (FLASH_STATUS)

Address offset: 0x04

Reset value: 0x0000 0000

Programming error flag.

0: ReadNo error.

WriteClear this flag.

1: Set by HW when

- Start to Erase/Program and find that the address is over page.

boundary

- Start to Erase/Program and find that the address is illegal. (>ROM

size)

- Fill in Data and the address is already over Page Boundary.

Busy flag.

0: Flash operation is not busy.

1: Flash operation is in progress. This is set on the beginning of a Flash

operation and reset when the operation finishes or when an error occurs

by HW.

11.11.3 Flash Control register (FLASH_CTRL)

Address offset: 0x08

Checksum calculation chosen.

This bit is set only by SW and reset when the BUSY bit resets.

Start Erase/Programming operation.

1: Triggers an Erase/Programming operation. This bit is set only by SW

and resets when the BUSY bit resets.

0: Stop/Finish operation.

Loading...

Loading...