SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 43 Version 1.5

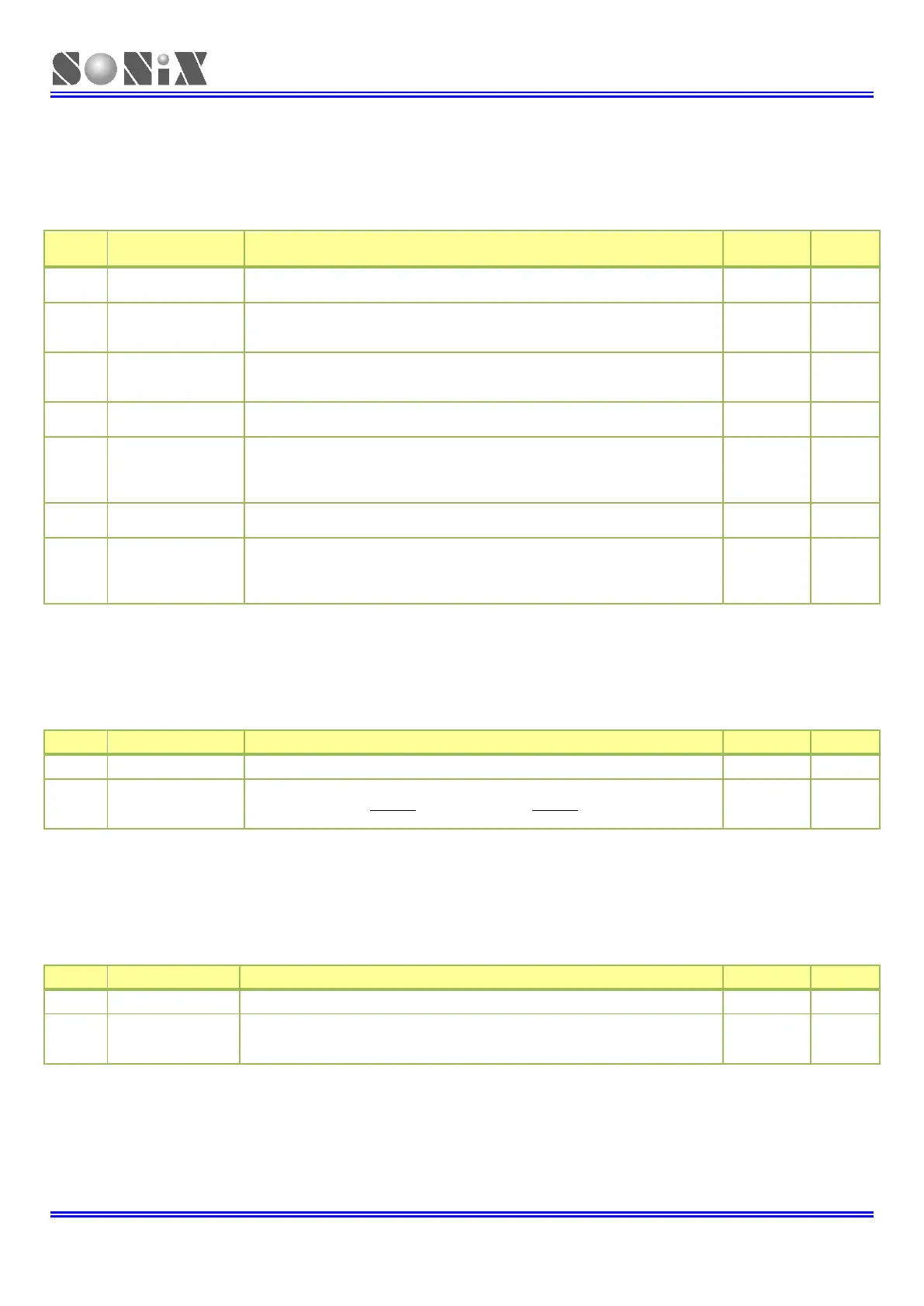

3.3.6 LVD Control register (SYS0_LVDCTRL)

Address Offset: 0x18

The LVD control register selects four separate threshold values for generating a LVD interrupt to the NVIC or LVD

reset.

LVD enable.

0: Disable.

1: Enable.

LVD Reset enable.

0: Disable Flag.

1: Enable Reset.

LVD interrupt level.

01: 2.40V.

10: 3.30V.

Other: Reserved.

LVD reset level.

010: 2.40V.

100: 3.30V.

Other: Reserved.

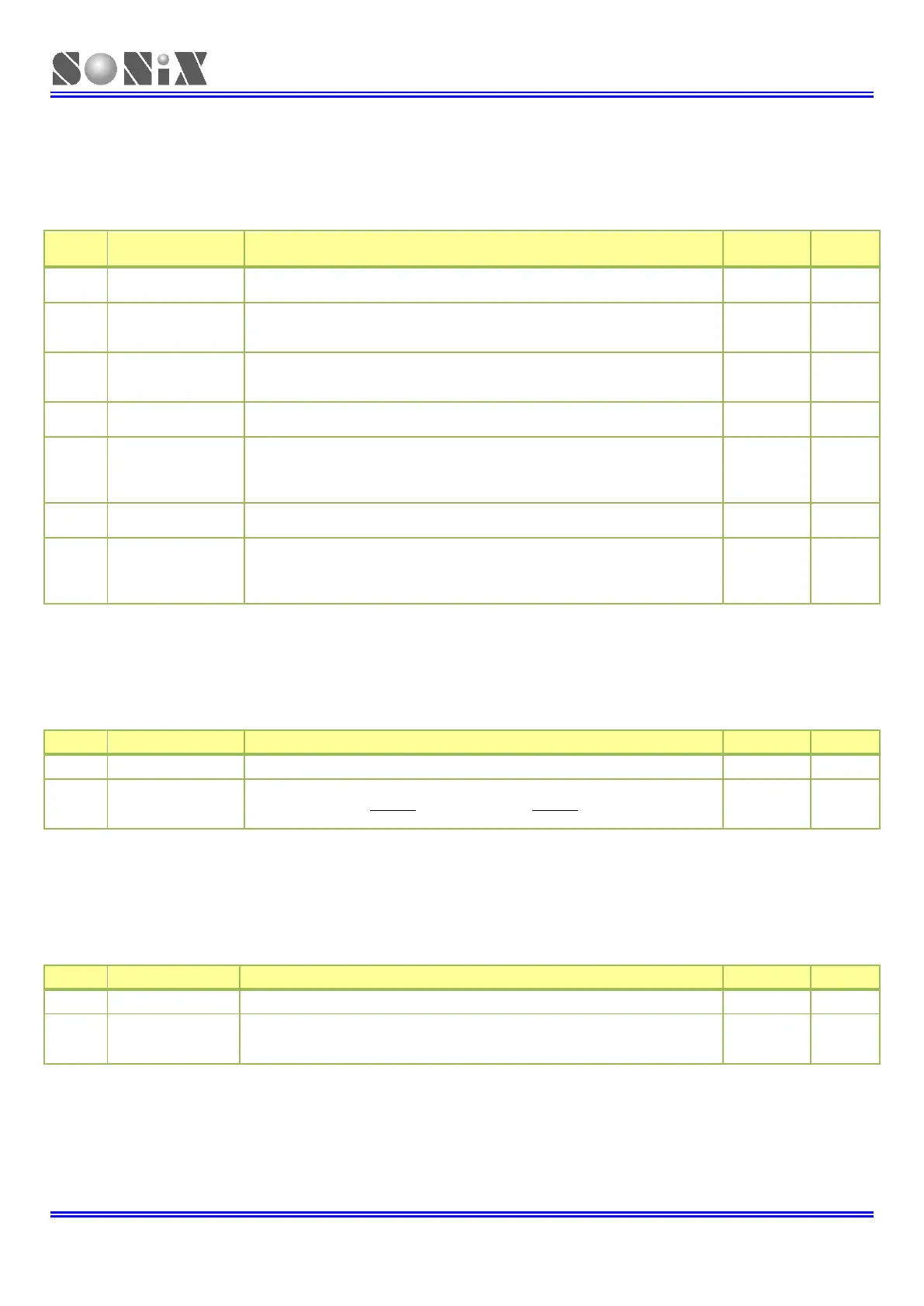

3.3.7 External RESET Pin Control register (SYS0_EXRSTCTRL)

Address Offset: 0x1C

External RESET pin disable bit.

0: Enable external RESET pin. (P3.8 acts as RESET pin)

1: Disable. (P3.8 acts as GPIO pin)

3.3.8 SWD Pin Control register (SYS0_SWDCTRL)

Address Offset: 0x20

SWD pin disable bit.

0: Enable SWD pin. (P3.7 acts as SWDIO pin, P3.6 acts as SWCLK pin)

1: Disable. (P3.7 and P3.6 act as GPIO pins)

Loading...

Loading...