SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 114 Version 1.5

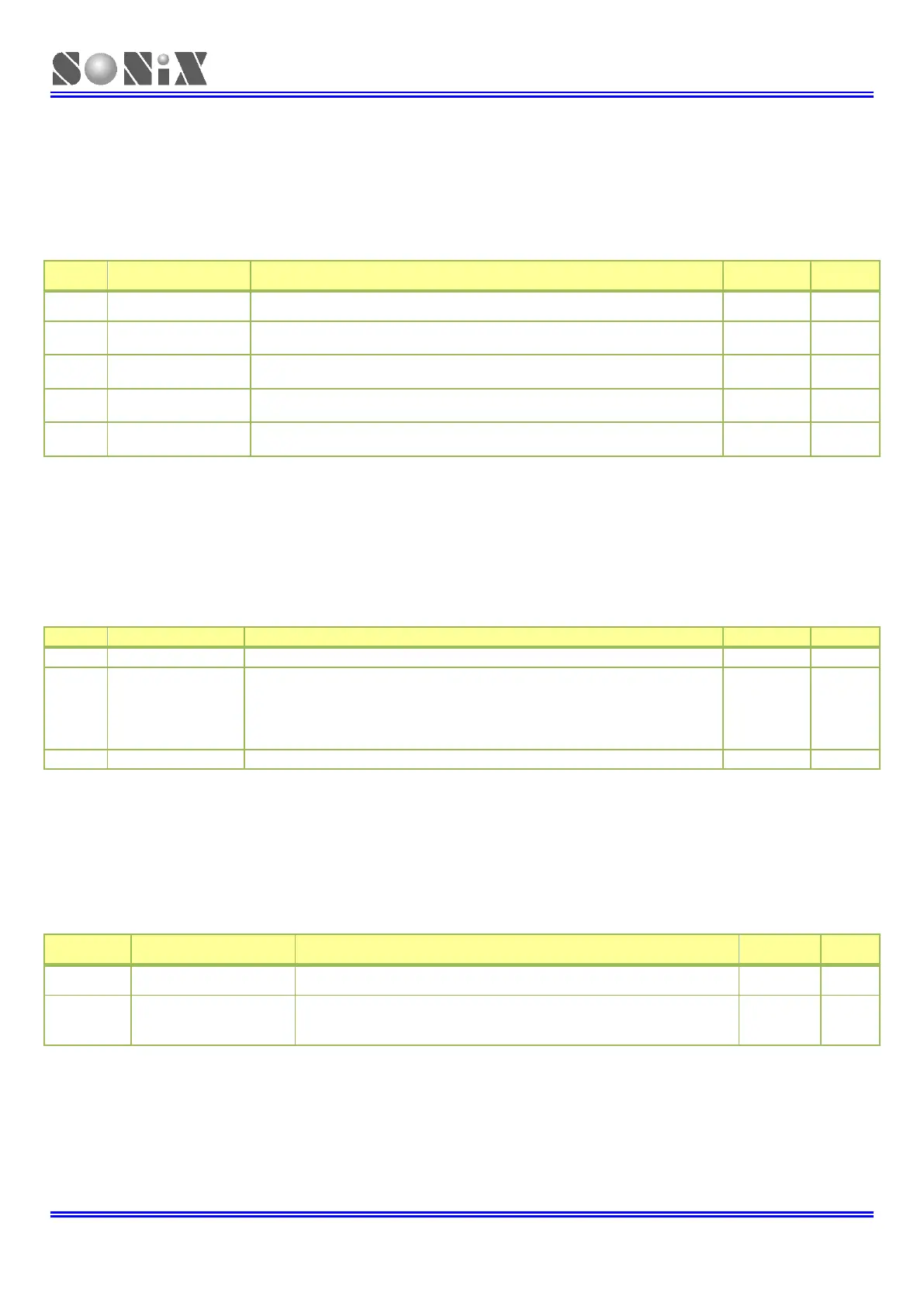

10.9.9 USB Endpoint Data Toggle Register (USB_EPTOGGLE)

Address Offset: 0x3C

Reset value: 0x0000 003F

0: Clear EP4‘s toggle bit to DATA0.

1: HW sets toggle bit automatically.

0: Clear EP3‘s toggle bit to DATA0.

1: HW sets toggle bit automatically.

0: Clear EP2‘s toggle bit to DATA0.

1: HW sets toggle bit automatically.

0: Clear EP1‘s toggle bit to DATA0.

1: HW sets toggle bit automatically.

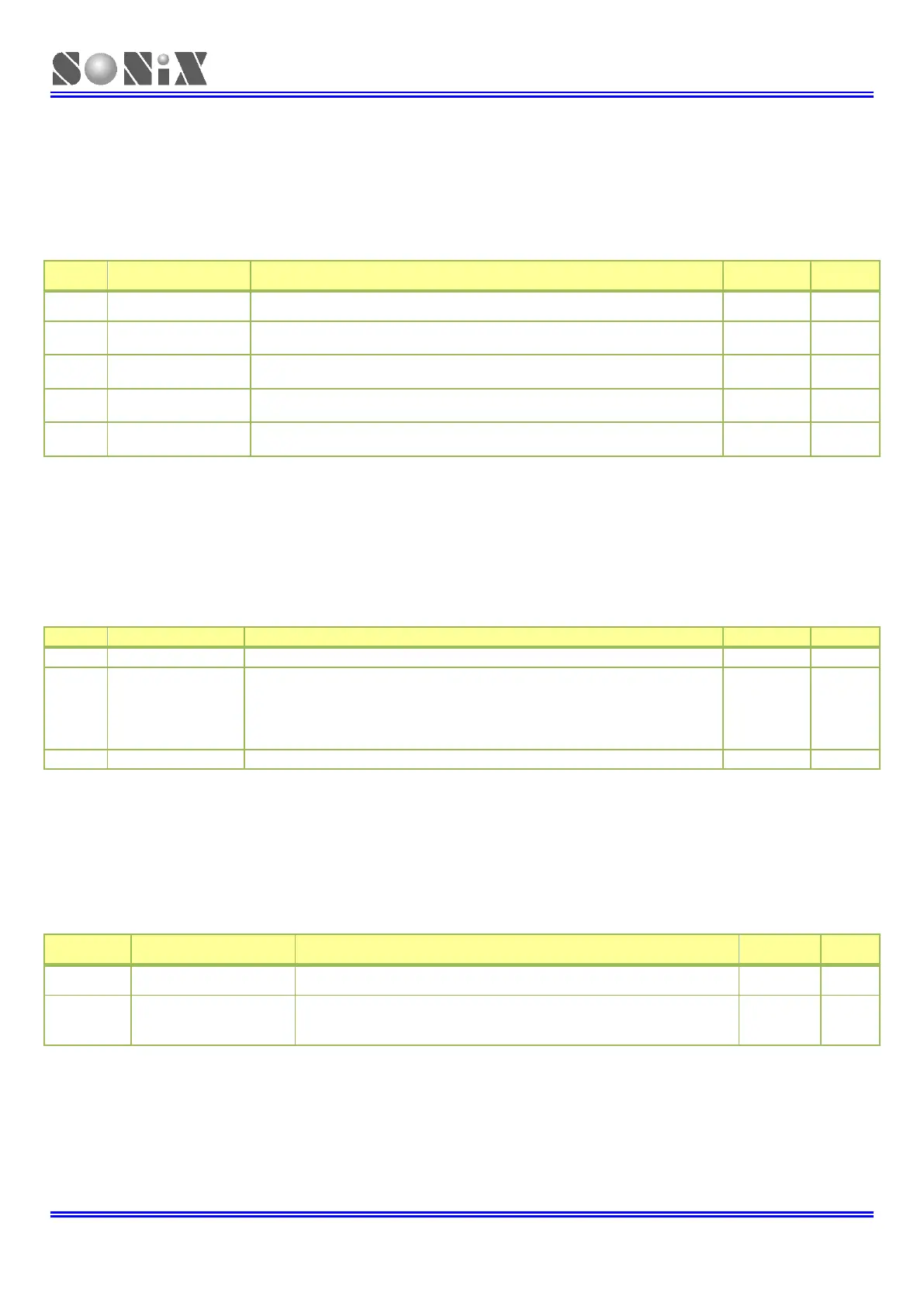

10.9.10 USB Endpoint n Buffer Offset Register (USB_EPnBUFOS, n = 1 ~ 4)

Address Offset: 0x48, 0x4C, 0x50, 0x54

Reset value: 0x0000 0000

The offset address for each endpoint data buffer.

The effective offset address is:

USB_SRAM address + {EPnBUFOS[7:2], 2’b00}

Where USB_SRAM address = USB_BA + 0x100

For endpoint 0, the offset address is fixed as USB_SRAM address.

10.9.11 USB Frame Number Register (USB_FRMNO)

Address Offset: 0x60

Reset value: 0x0000 0000

The 11-bit frame number of the Start-Of-Frame(SOF) packet. This

number is updated by H/W automatically when SOF packet is

received.

10.9.12 USB PHY Parameter Register (USB_PHYPRM)

Address Offset: 0x64

Reset value: 0x0000 0000

Loading...

Loading...