SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 64 Version 1.5

6.7 CT16Bn REGISTERS

Base Address: 0x4000 0000 (CT16B0)

0x4000 2000 (CT16B1)

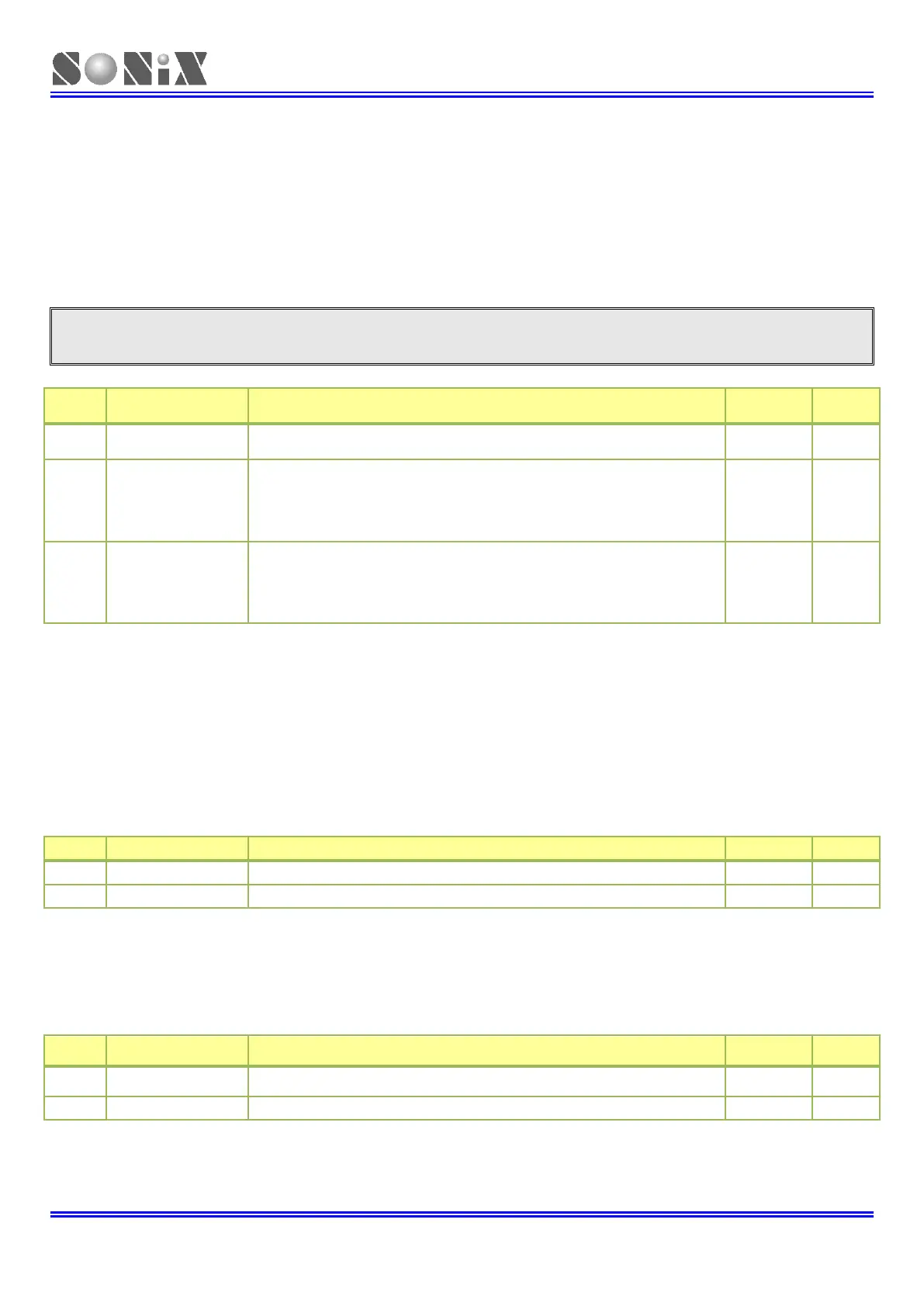

6.7.1 CT16Bn Timer Control register (CT16Bn_TMRCTRL) (n=0,1)

Address Offset: 0x00

Note: In order to initial TC and PC correctly, SW shall reset TC and PC by setting CRST to 1, and then

enable counter by setting CRST to 1.

Counter Reset.

0: Disable counter reset.

1: Timer Counter and the Prescale Counter are synchronously reset on

the next positive edge of PCLK. This is cleared by HW when the counter

reset operation finishes.

Counter Enable

0: Disable Counter.

1: Enable Timer Counter and Prescale Counter for counting.

CEN bit shall be set at last!

* Always Edge-aligned Up-counting mode

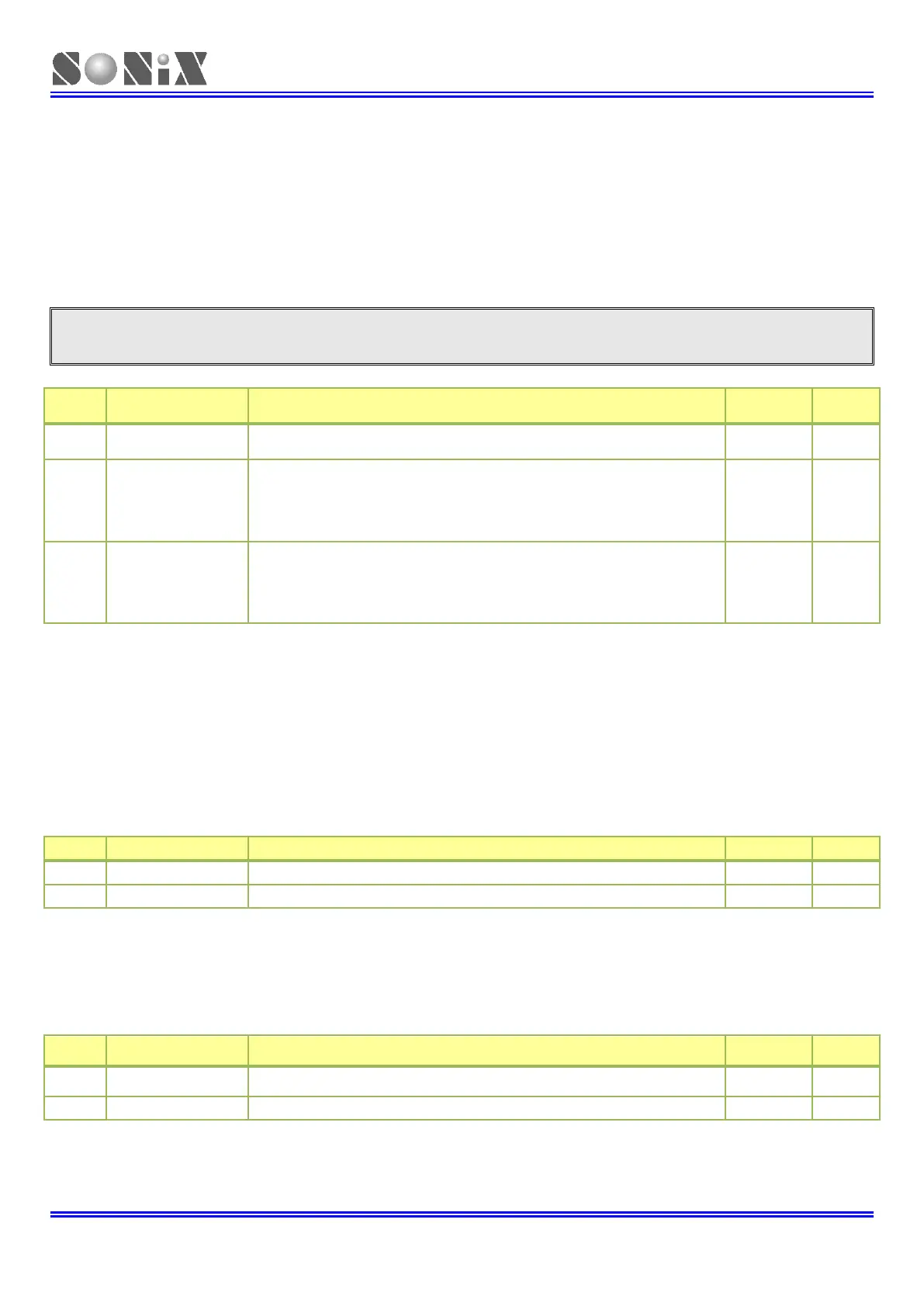

6.7.2 CT16Bn Timer Counter register (CT16Bn_TC) (n=0,1)

Address Offset: 0x04

The 16-bit Timer Counter is incremented when the Prescale Counter reaches its terminal count. Unless it is reset

before reaching its upper limit, the TC will count up to the value 0x0000FFFF and then wrap back to the value

0x00000000. This event does not cause an interrupt, but a Match register can be used to detect an overflow if needed.

6.7.3 CT16Bn Prescale register (CT16Bn_PRE) (n=0,1)

Address Offset: 0x08

Loading...

Loading...