SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 86 Version 1.5

7.3 WDT REGISTERS

Base Address: 0x4001 0000

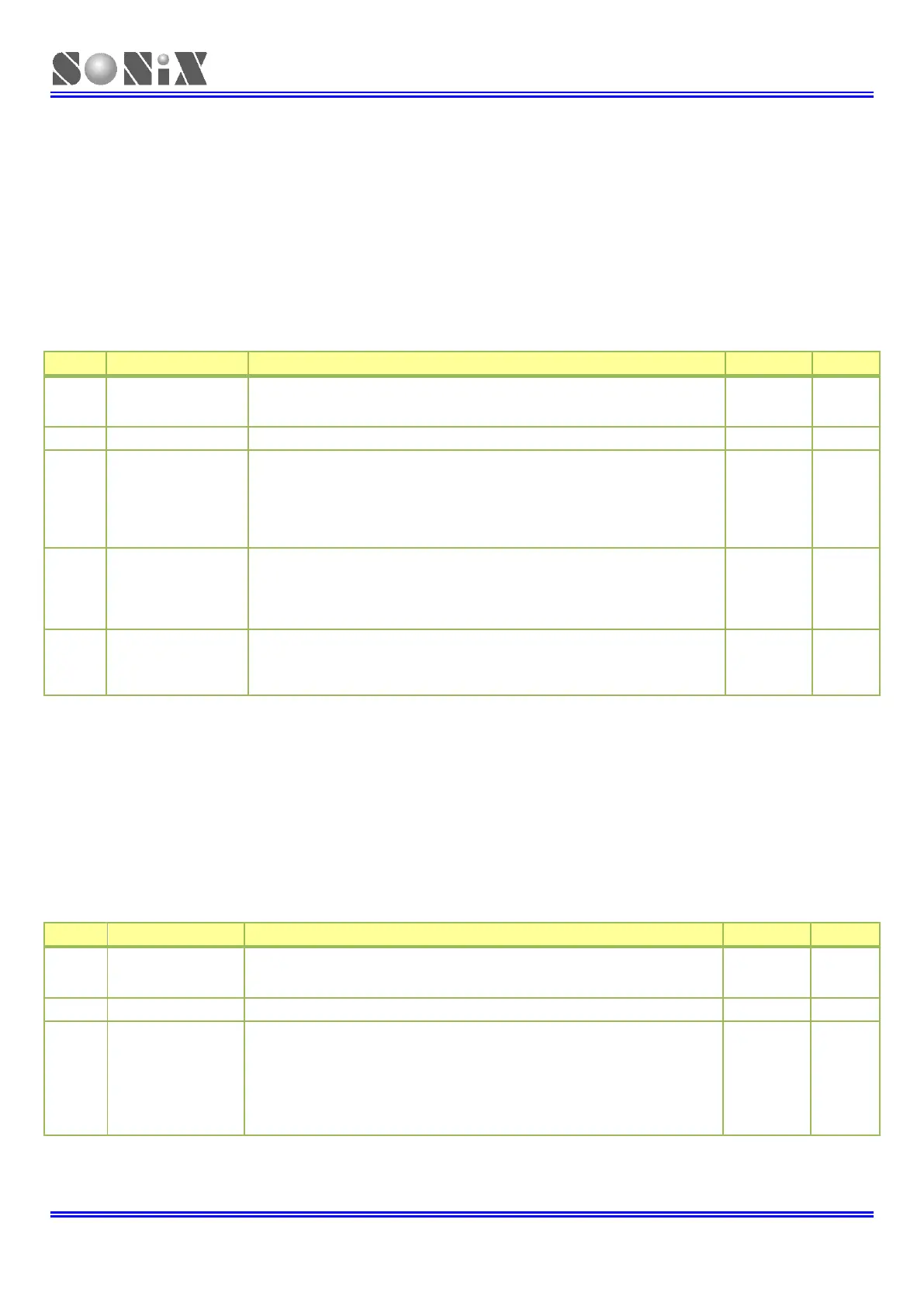

7.3.1 Watchdog Configuration register (WDT_CFG)

Address Offset: 0x00

The WDT_CFG register controls the operation of the Watchdog through the combination of WDTEN and WDTIE bits.

This register indicates the raw status for Watchdog Timer interrupts. A WDT interrupt is sent to the interrupt controller if

both the WDINT bit and the WDTIE bit are set.

Watchdog register key.

Read as 0. When writing to the register you must write 0x5AFA to

WDKEY, otherwise behavior of writing to the register is ignored.

Watchdog interrupt flag.

<Read>

0: Watchdog does not cause an interrupt.

1: Watchdog time-out and causes an interrupt (Only when WDTIE =1).

<Write>

0: Clear this flag. SW shall feed Watchdog before clearing.

Watchdog interrupt enable.

0: Watchdog timeout will cause a chip reset. (Watchdog reset mode)

Watchdog counter underflow will reset the MCU, and will clear the

WDINT flag.

1: Watchdog timeout will cause an interrupt. (Watchdog interrupt mode)

Watchdog enable.

0: Disable.

1: Enable. When enable the watchdog, the WDT_TC value is loaded in the

watchdog counter.

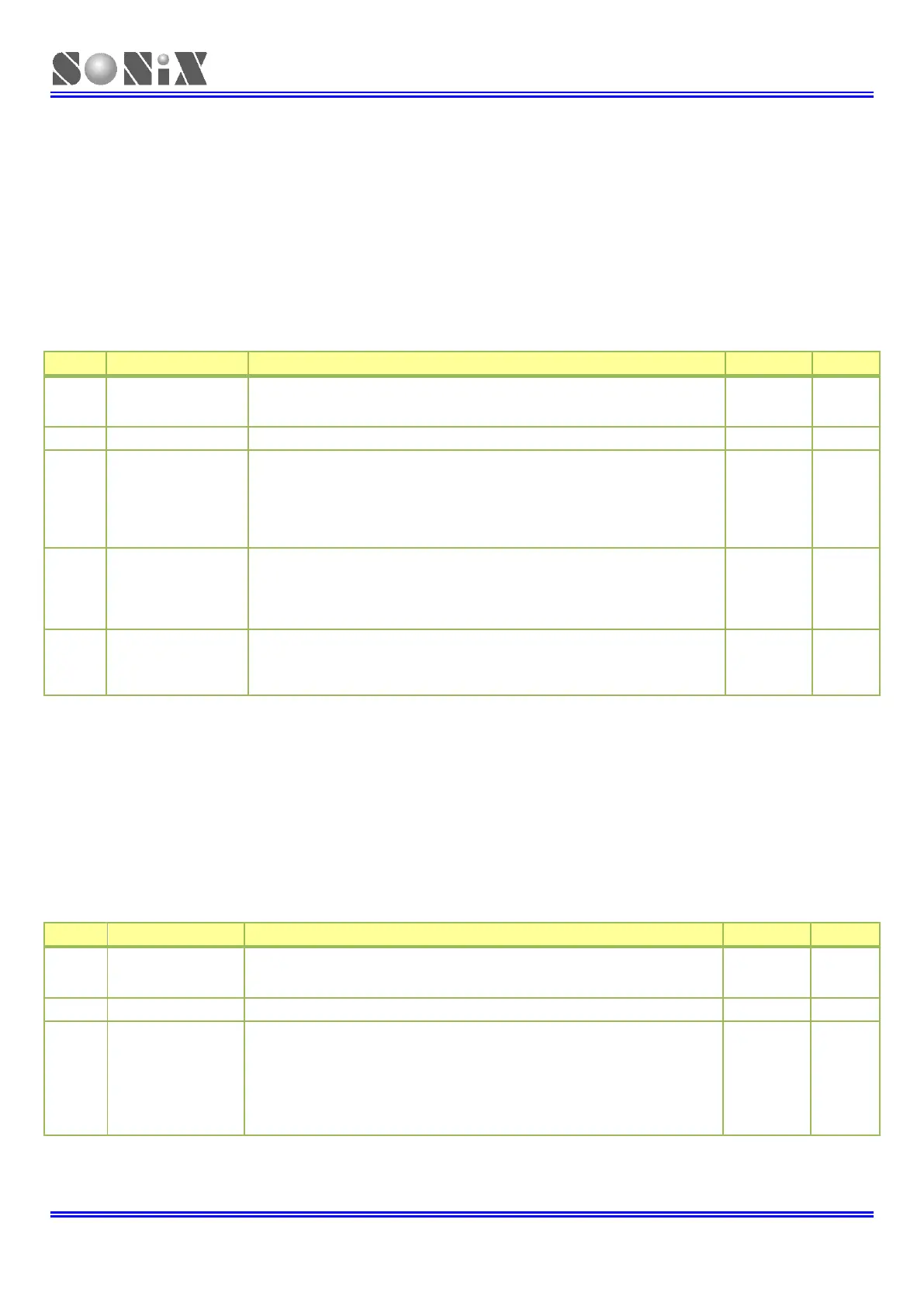

7.3.2 Watchdog Timer Constant register (WDT_TC)

Address Offset: 0x08

The WDT_TC register determines the time-out value. Every time a feed sequence occurs the WDT_TC content is

reloaded in to the Watchdog timer. It’s an 8-bit counter. Thus the time-out interval is T

WDT_PCLK

× 128 x 1 ~ T

WDT_PCLK

×

128 x 256.

Watchdog overflow time = (31.25us x 1) x 128 x 1 ~ (31.25us x 32) x 128 x 256

= 4ms ~32768ms

Watchdog register key.

Read as 0. When writing to the register you must write 0x5AFA to

WDKEY, otherwise behavior of writing to the register is ignored.

Watchdog timer constant reload value = TC[7:0]+1

0000 0000 : Timer constant = 1

0000 0001 : Timer constant = 2

……….

……….

1111 1110 : Timer constant = 255

1111 1111 : Timer constant = 256

Watchdog clock source is fixed as ILRC.

Loading...

Loading...