SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 47 Version 1.5

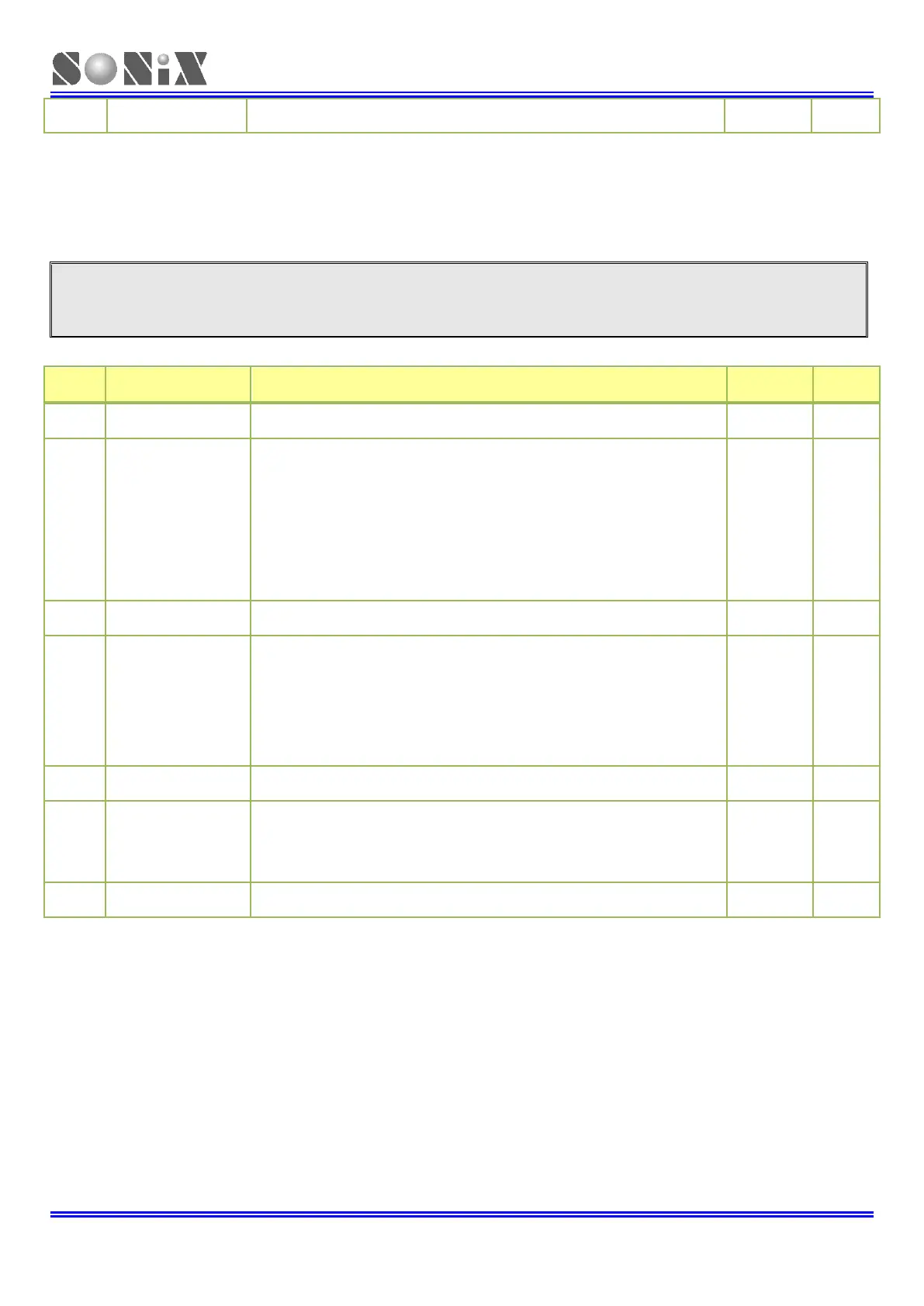

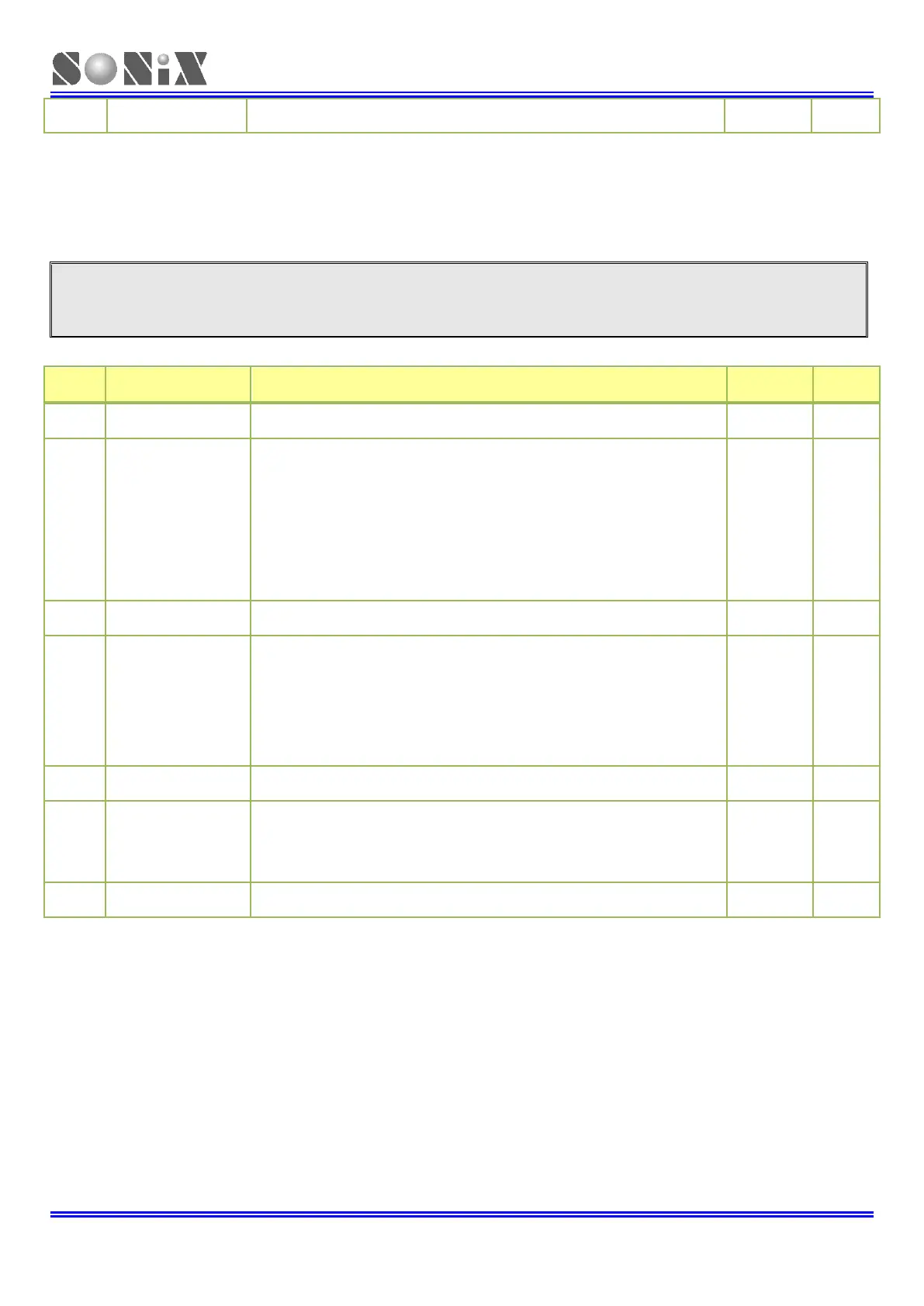

3.4.2 APB Clock Prescale register 1 (SYS1_APBCP1)

Address Offset: 0x08

Note: Must reset the corresponding peripheral with SYS1_PRST register after changing the prescale

value.

CT16B2 clock source prescaler

I2C1 clock source prescaler

Clock-out source prescaler.

000: Clock-out source / 1.

001: Clock-out source / 2.

010: Clock-out source / 4.

011: Clock-out source / 8.

100: Clock-out source / 16.

101: Clock-out source / 32.

110: Clock-out source / 64.

111: Clock-out source / 128.

Other: Reserved

WDT clock source prescaler.

000: WDT_PCLK = WDT clock source / 1.

001: WDT_PCLK = WDT clock source / 2.

010: WDT_PCLK = WDT clock source / 4.

011: WDT_PCLK = WDT clock source / 8.

100: WDT_PCLK = WDT clock source / 16.

101: WDT_PCLK = WDT clock source / 32.

Other: Reserved

SysTick clock source prescaler

00: SysTick_PCLK = HCLK / 1.

01: SysTick_PCLK = HCLK / 2.

10: SysTick_PCLK = HCLK / 4.

11: SysTick_PCLK = HCLK / 8.

Loading...

Loading...