SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 68 Version 1.5

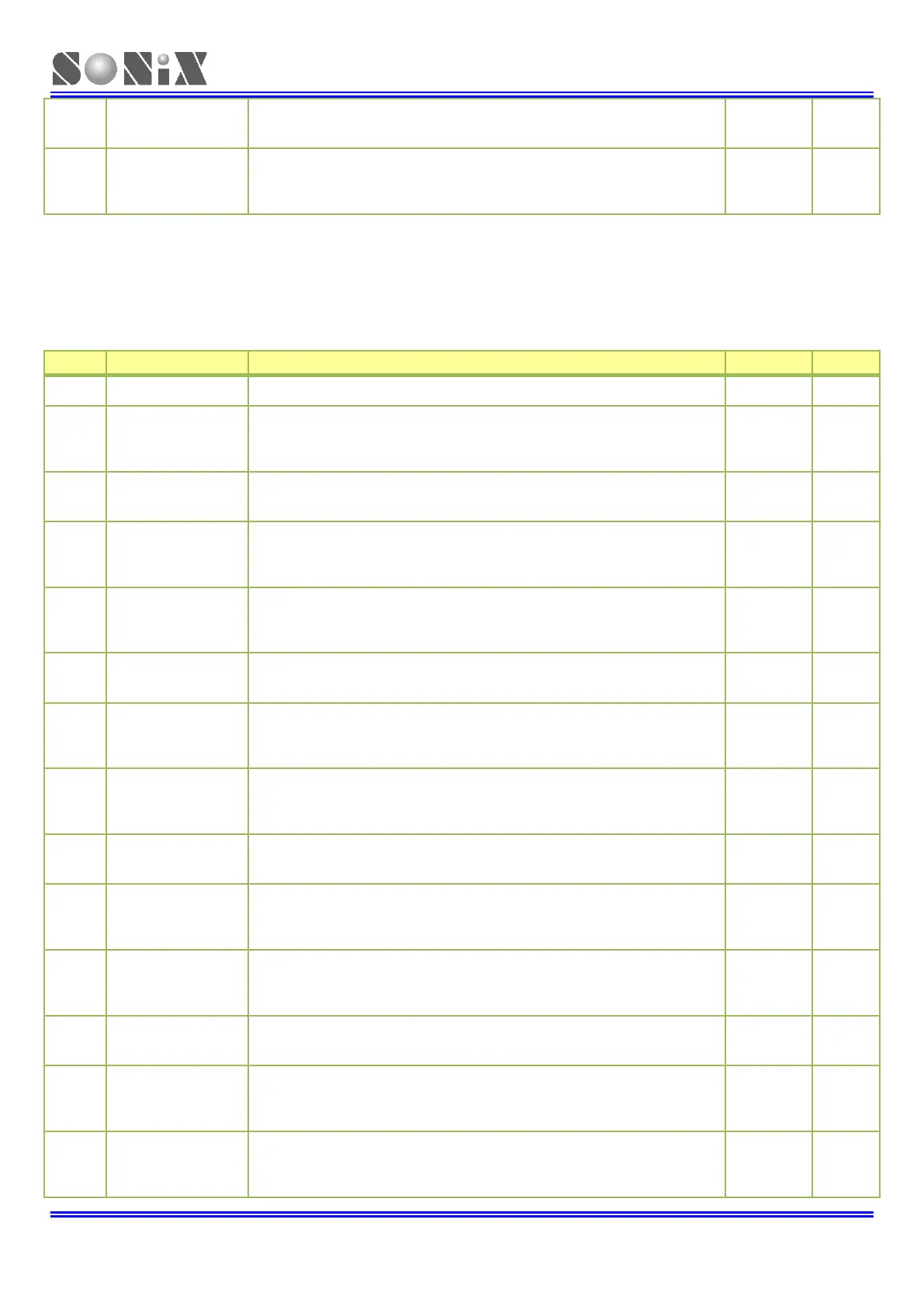

Enable reset TC when MR0 matches TC.

0: Disable.

1: Enable.

Enable generating an interrupt based on CM[2:0] when MR0 matches the

value in the TC.

0: Disable.

1: Enable.

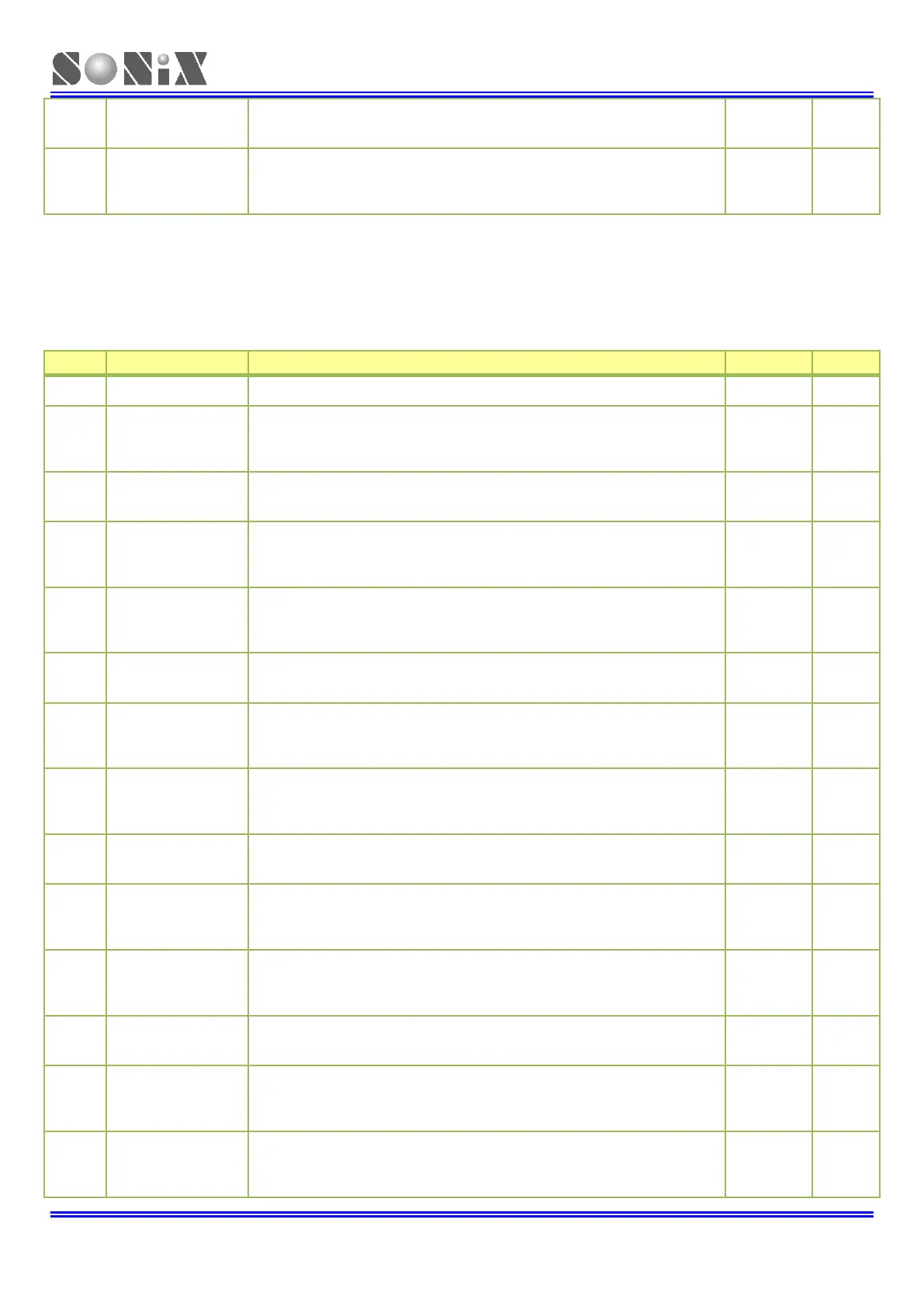

6.7.8 CT16Bn Match Control register 2(CT16Bn_MCTRL2) (n=1)

Address Offset: 0x18

Stop MR19: TC and PC will stop and CEN bit will be cleared if MR19

matches TC.

0: Disable.

1: Enable.

Enable reset TC when MR19 matches TC.

0: Disable.

1: Enable.

Enable generating an interrupt based on CM[2:0] when MR19 matches the

value in the TC.

0: Disable.

1: Enable.

Stop MR18: TC and PC will stop and CEN bit will be cleared if MR18

matches TC.

0: Disable.

1: Enable.

Enable reset TC when MR18 matches TC.

0: Disable.

1: Enable.

Enable generating an interrupt based on CM[2:0] when MR18 matches the

value in the TC.

0: Disable.

1: Enable.

Stop MR17: TC and PC will stop and CEN bit will be cleared if MR17

matches TC.

0: Disable.

1: Enable.

Enable reset TC when MR17 matches TC.

0: Disable.

1: Enable.

Enable generating an interrupt based on CM[2:0] when MR17 matches the

value in the TC.

0: Disable.

1: Enable.

Stop MR16: TC and PC will stop and CEN bit will be cleared if MR16

matches TC.

0: Disable.

1: Enable.

Enable reset TC when MR16 matches TC.

0: Disable.

1: Enable.

Enable generating an interrupt based on CM[2:0] when MR16 matches the

value in the TC.

0: Disable.

1: Enable.

Stop MR15: TC and PC will stop and CEN bit will be cleared if MR15

matches TC.

0: Disable.

1: Enable.

Loading...

Loading...