32 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 1: Introduction to the RocketIO GTP Transceiver

R

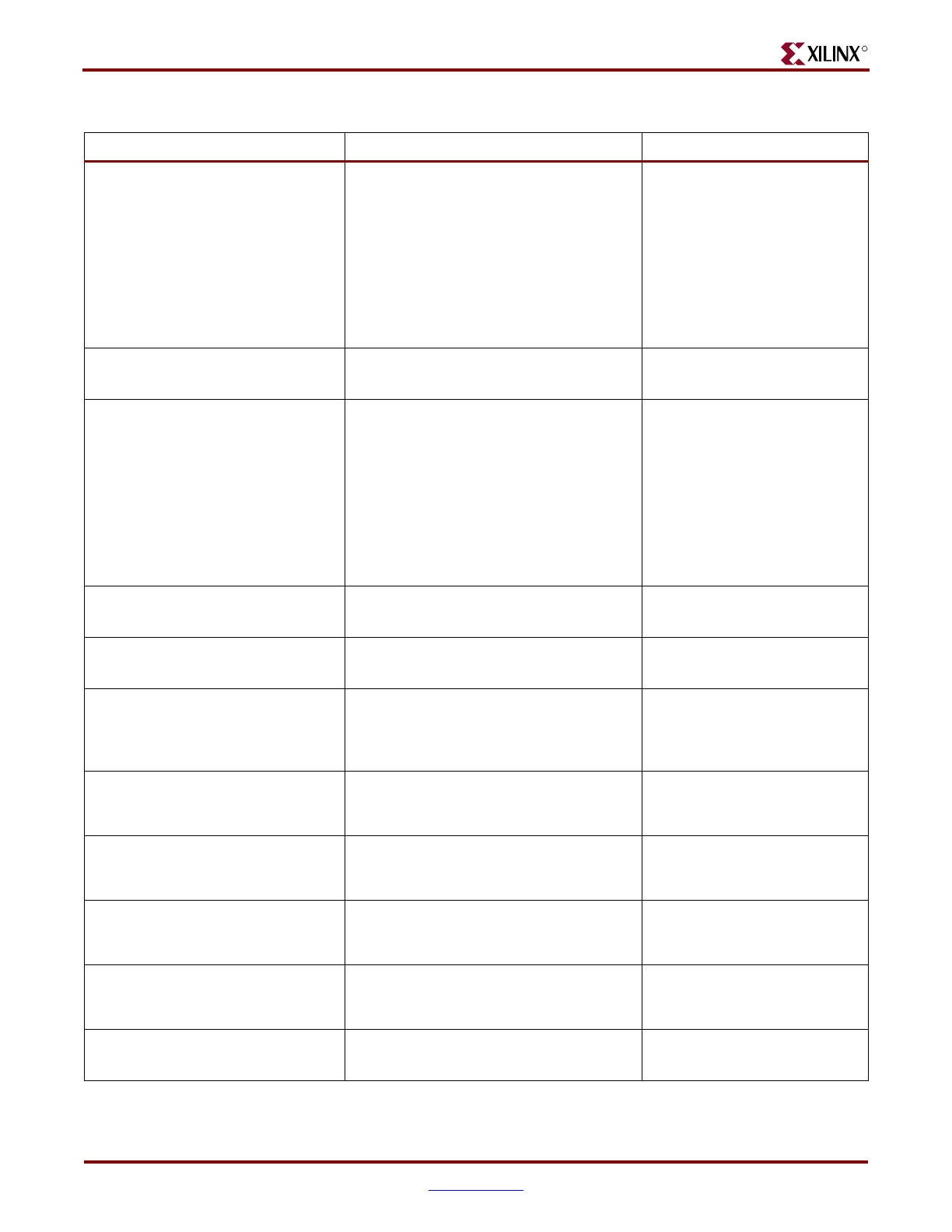

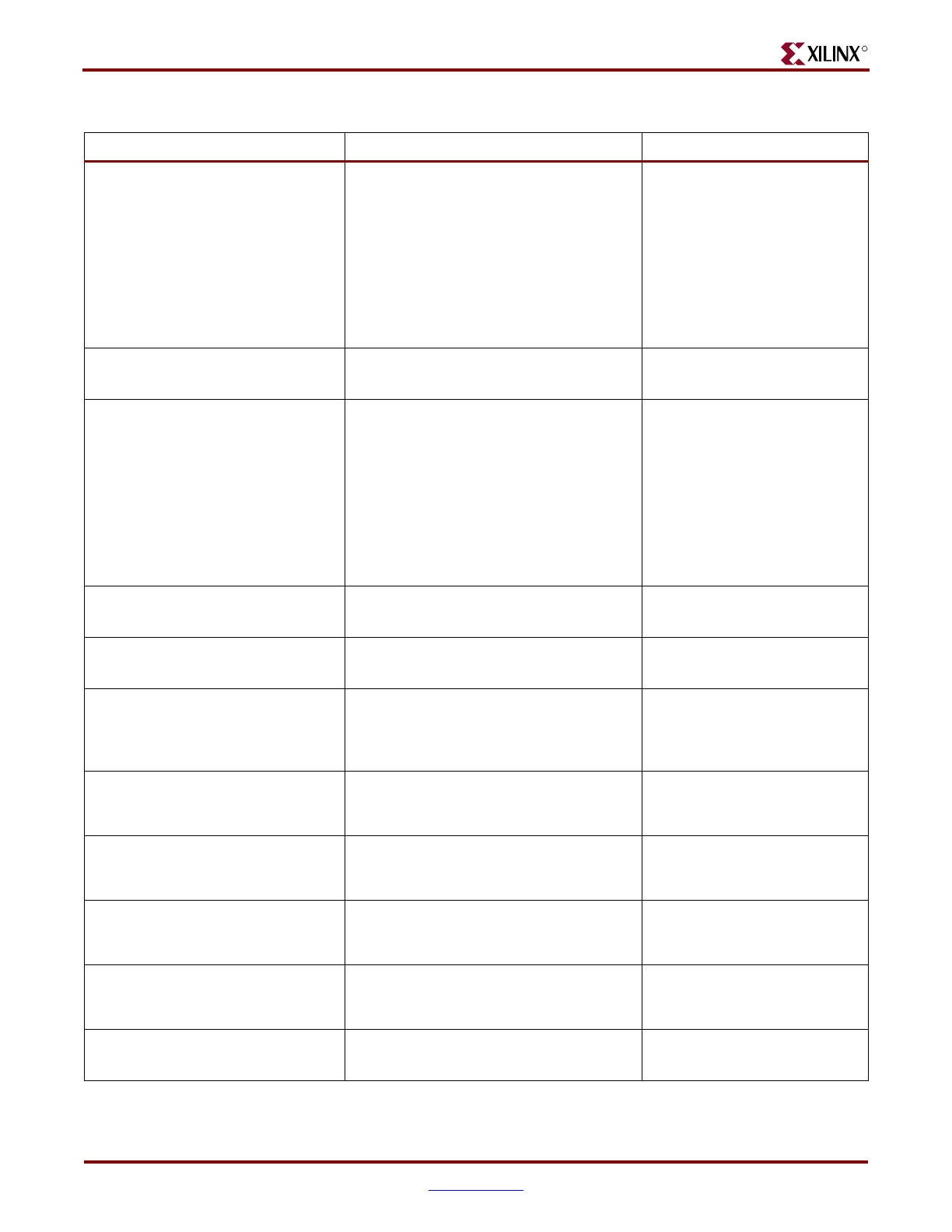

CHAN_BOND_SEQ_1_1_0

CHAN_BOND_SEQ_1_1_1

CHAN_BOND_SEQ_1_2_0

CHAN_BOND_SEQ_1_2_1

CHAN_BOND_SEQ_1_3_0

CHAN_BOND_SEQ_1_3_1

CHAN_BOND_SEQ_1_4_0

CHAN_BOND_SEQ_1_4_1

Used in conjunction with

CHAN_BOND_SEQ_1_ENABLE to define

channel bonding sequence 1.

Configurable Channel Bonding

(Lane Deskew) (page 177)

CHAN_BOND_SEQ_1_ENABLE_0

CHAN_BOND_SEQ_1_ENABLE_1

Sets which parts of channel bonding

sequence 1 are don't cares.

Configurable Channel Bonding

(Lane Deskew) (page 177)

CHAN_BOND_SEQ_2_1_0

CHAN_BOND_SEQ_2_1_1

CHAN_BOND_SEQ_2_2_0

CHAN_BOND_SEQ_2_2_1

CHAN_BOND_SEQ_2_3_0

CHAN_BOND_SEQ_2_3_1

CHAN_BOND_SEQ_2_4_0

CHAN_BOND_SEQ_2_4_1

Used in conjunction with

CHAN_BOND_SEQ_2_ENABLE to define

the second channel bonding sequence.

Configurable Channel Bonding

(Lane Deskew) (page 177)

CHAN_BOND_SEQ_2_ENABLE_0

CHAN_BOND_SEQ_2_ENABLE_1

Sets which parts of channel bonding

sequence 2 are don't cares.

Configurable Channel Bonding

(Lane Deskew) (page 177)

CHAN_BOND_SEQ_2_USE_0

CHAN_BOND_SEQ_2_USE_1

Determines if the second channel bonding

sequence is to be used.

Configurable Channel Bonding

(Lane Deskew) (page 177)

CHAN_BOND_SEQ_LEN_0

CHAN_BOND_SEQ_LEN_1

Defines the length in bytes of the channel

bonding sequence that the transceiver

matches to detect opportunities for channel

bonding.

Configurable Channel Bonding

(Lane Deskew) (page 178)

CLK_COR_ADJ_LEN_0

CLK_COR_ADJ_LEN_1

Defines the size of the adjustment (number

of bytes repeated or skipped) in a clock

correction.

Configurable Clock Correction

(page 169)

CLK_COR_DET_LEN_0

CLK_COR_DET_LEN_1

Defines the length of the sequence that the

transceiver matches to detect opportunities

for clock correction.

Configurable Clock Correction

(page 170)

CLK_COR_INSERT_IDLE_FLAG_0

CLK_COR_INSERT_IDLE_FLAG_1

Controls whether RXRUNDISP input status

indicates running disparity or inserted-idle

(clock correction sequence) flag.

Configurable Clock Correction

(page 170)

CLK_COR_KEEP_IDLE_0

CLK_COR_KEEP_IDLE_1

Controls whether the elastic buffer must

retain at least one clock correction sequence

in the byte stream.

Configurable Clock Correction

(page 170)

CLK_COR_MAX_LAT_0

CLK_COR_MAX_LAT_1

Specifies the maximum elastic buffer

latency.

Configurable Clock Correction

(page 170)

Table 1-4: GTP_DUAL Attribute Summary (Continued)

Attribute Description Section (Page)

Loading...

Loading...