Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 33

UG196 (v1.3) May 25, 2007

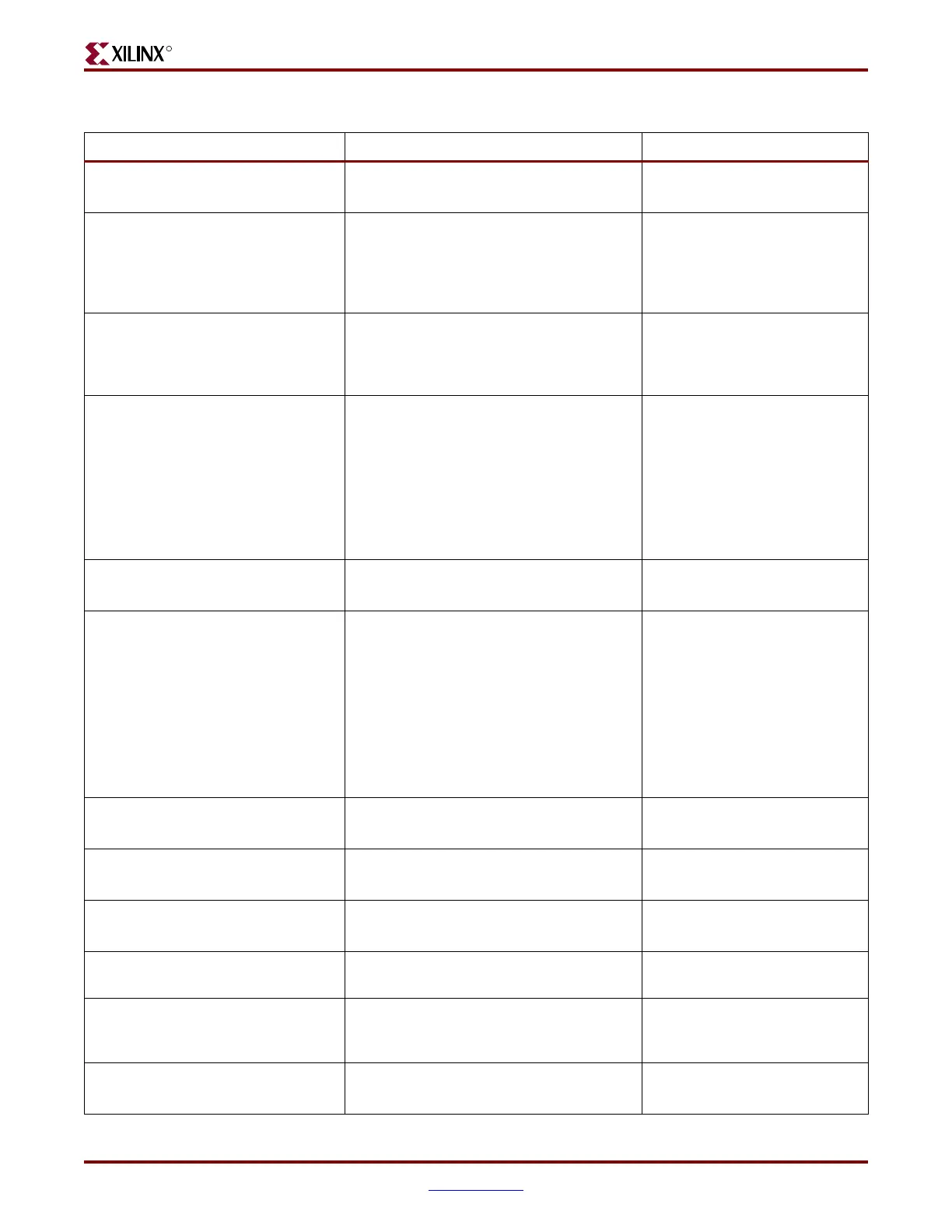

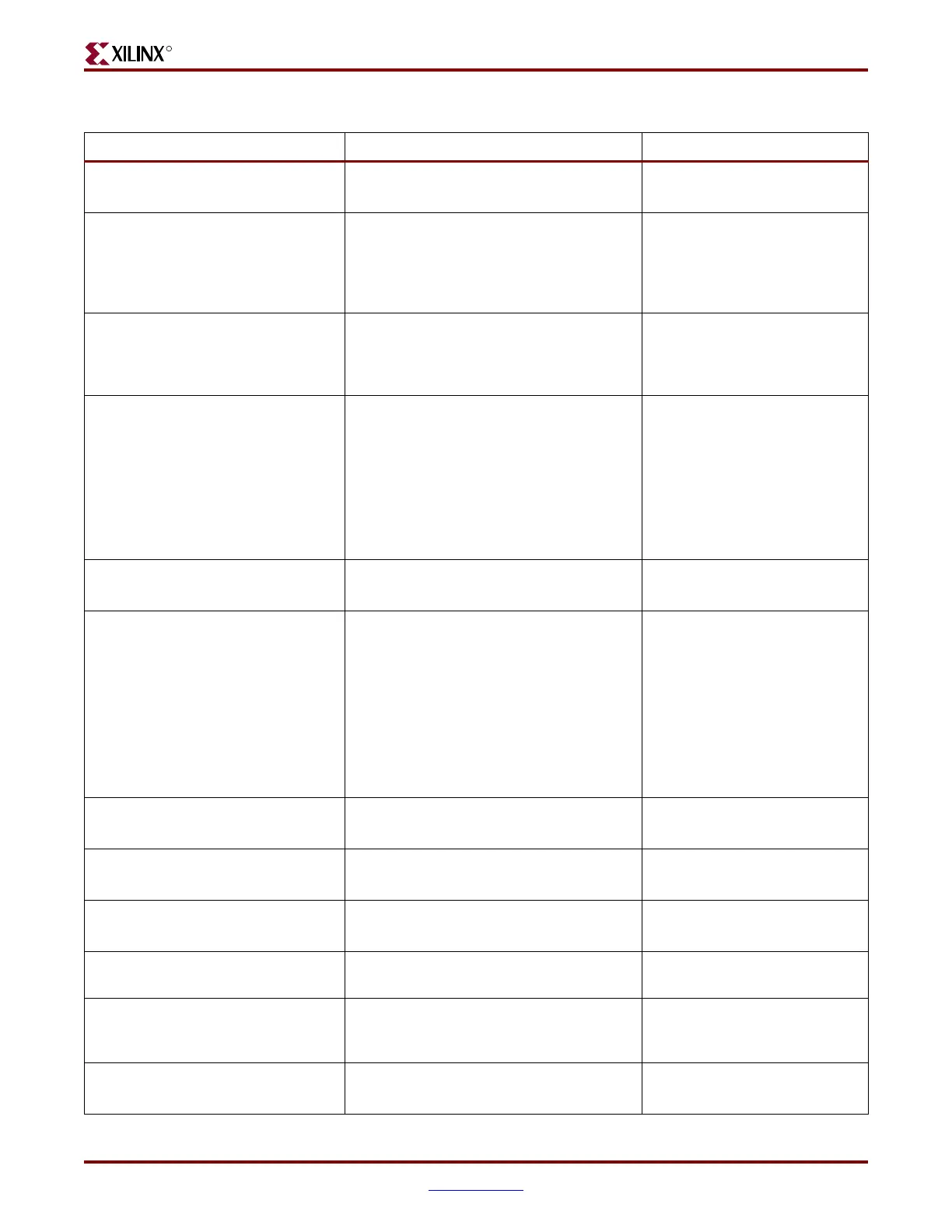

Ports and Attributes

R

CLK_COR_MIN_LAT_0

CLK_COR_MIN_LAT_1

Specifies the minimum elastic buffer latency.

Configurable Clock Correction

(page 170)

CLK_COR_PRECEDENCE_0

CLK_COR_PRECEDENCE_1

Determines whether clock correction or

channel bonding takes precedence when

both operations are triggered at the same

time. Set to TRUE to give clock correction

precedence.

Configurable Clock Correction

(page 170)

CLK_COR_REPEAT_WAIT_0

CLK_COR_REPEAT_WAIT_1

Specifies the minimum number of

RXUSRCLK cycles without clock correction

that must occur between successive clock

corrections.

Configurable Clock Correction

(page 170)

CLK_COR_SEQ_1_1_0

CLK_COR_SEQ_1_1_1

CLK_COR_SEQ_1_2_0

CLK_COR_SEQ_1_2_1

CLK_COR_SEQ_1_3_0

CLK_COR_SEQ_1_3_1

CLK_COR_SEQ_1_4_1

The CLK_COR_SEQ_1 attributes are used

in conjunction with

CLK_COR_SEQ_1_ENABLE to define

clock correction sequence 1.

Configurable Clock Correction

(page 172)

CLK_COR_SEQ_1_ENABLE_0

CLK_COR_SEQ_1_ENABLE_1

Sets which parts of clock correction

sequence 1 are don't cares.

Configurable Clock Correction

(page 172)

CLK_COR_SEQ_2_1_0

CLK_COR_SEQ_2_1_1

CLK_COR_SEQ_2_2_0

CLK_COR_SEQ_2_2_1

CLK_COR_SEQ_2_3_0

CLK_COR_SEQ_2_3_1

CLK_COR_SEQ_2_4_0

CLK_COR_SEQ_2_4_1

Used in conjunction with

CLK_COR_SEQ_2_ENABLE to define the

second clock correction sequence.

Configurable Clock Correction

(page 172)

CLK_COR_SEQ_2_ENABLE_0

CLK_COR_SEQ_2_ENABLE_1

Sets which parts of clock correction

sequence 2 are don't cares.

Configurable Clock Correction

(page 172)

CLK_COR_SEQ_2_USE_0

CLK_COR_SEQ_2_USE_1

Determines if the second clock correction

sequence is to be used.

Configurable Clock Correction

(page 172)

CLK_CORRECT_USE_0

CLK_CORRECT_USE_1

Set to TRUE to enable Clock Correction.

Configurable Clock Correction

(page 172)

CLK25_DIVIDER

Sets the divider used to divide CLKIN

down to an internal rate close to 25 MHz.

Clocking (page 70), Power

Control (page 82)

CLKINDC_B

Must be set to TRUE. Oscillators driving the

dedicated reference clock inputs must be

AC coupled.

Clocking (page 70)

COM_BURST_VAL_0[3:0]

COM_BURST_VAL_1[3:0]

Number of bursts transmitted for a SATA

COM sequence.

TX OOB/Beacon Signaling

(page 120)

Table 1-4: GTP_DUAL Attribute Summary (Continued)

Attribute Description Section (Page)

Loading...

Loading...