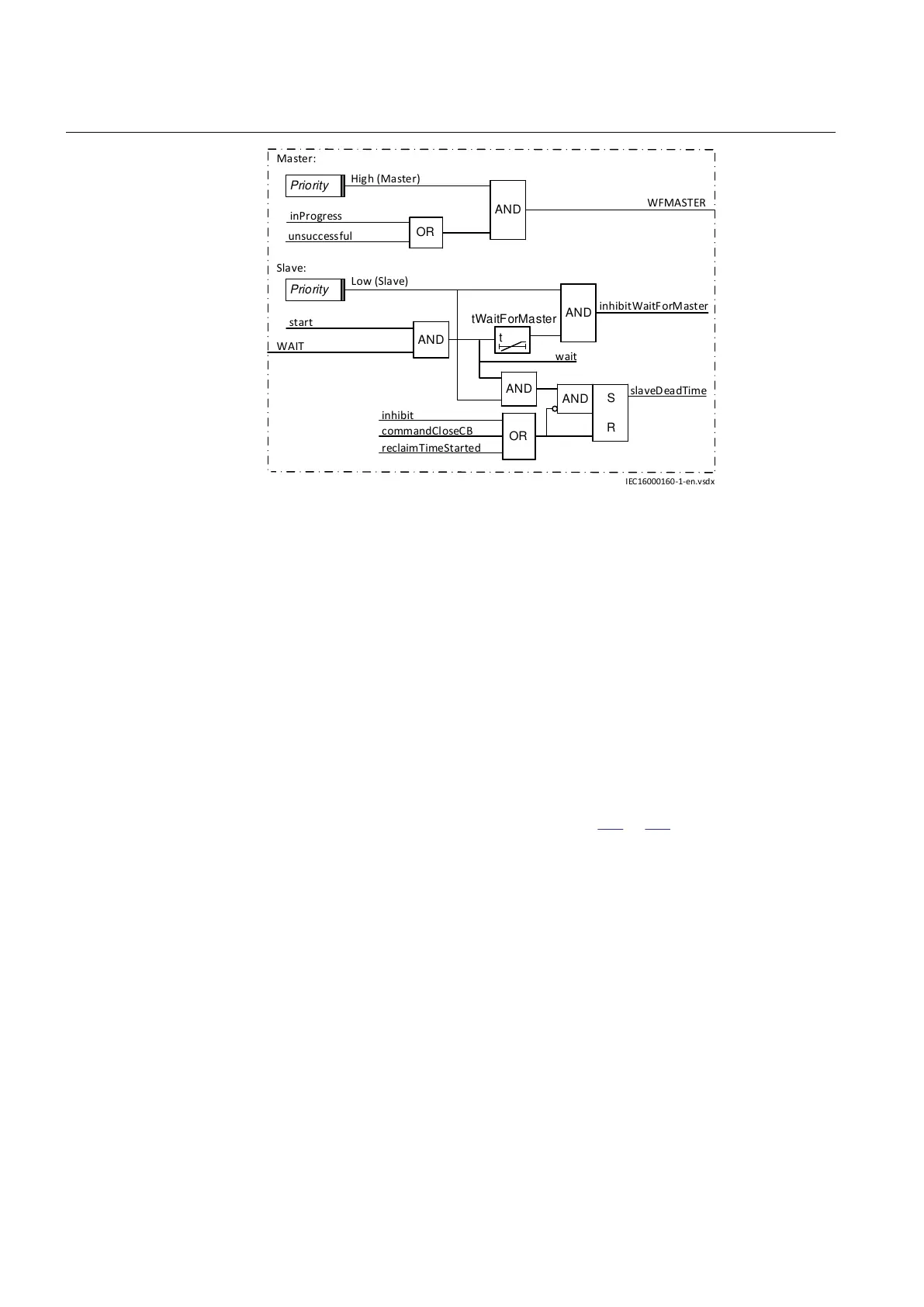

IEC16000160-1-en.vsdx

Priority

AND

OR

High (Master)

inProgress

unsuccessful

WFMASTER

Master:

Slave:

Priority

Low (Slave)

AND

AND

start

WAIT

t

tWaitForMaster

AND

AND

S

R

OR

inhibit

commandCloseCB

reclaimTimeStarted

inhibitWaitForMaster

slaveDeadTime

wait

IEC16000160 V1 EN-US

Figure 183: Master-Slave

If reclosing of the first circuit breaker is unsuccessful, the UNSUCCL output

connected to the INHIBIT input of the slave unit interrupts the reclosing sequence

of the latter. The signals can be cross-connected to allow simple changing of the

priority by just setting the High and the Low priorities without changing the

configuration. The CBCLOSED inputs from each circuit breaker are important in

multi-breaker arrangements to ensure that the circuit breaker was closed at the

beginning of the sequence. If the High priority breaker was not closed its auto

reclosing sequence will not start and the low priority breaker will just continue its

auto reclosing sequence in accordance with its normal settings.

11.2.6.5 Time sequence diagrams

M12458-10 v5

Some examples of the timing of internal and external signals at typical transient

and permanent faults are shown below in Figure

184 to 187.

Section 11 1MRK 506 382-UEN A

Control

374 Line distance protection REL650 2.2 IEC

Technical manual

Loading...

Loading...