— 70 —

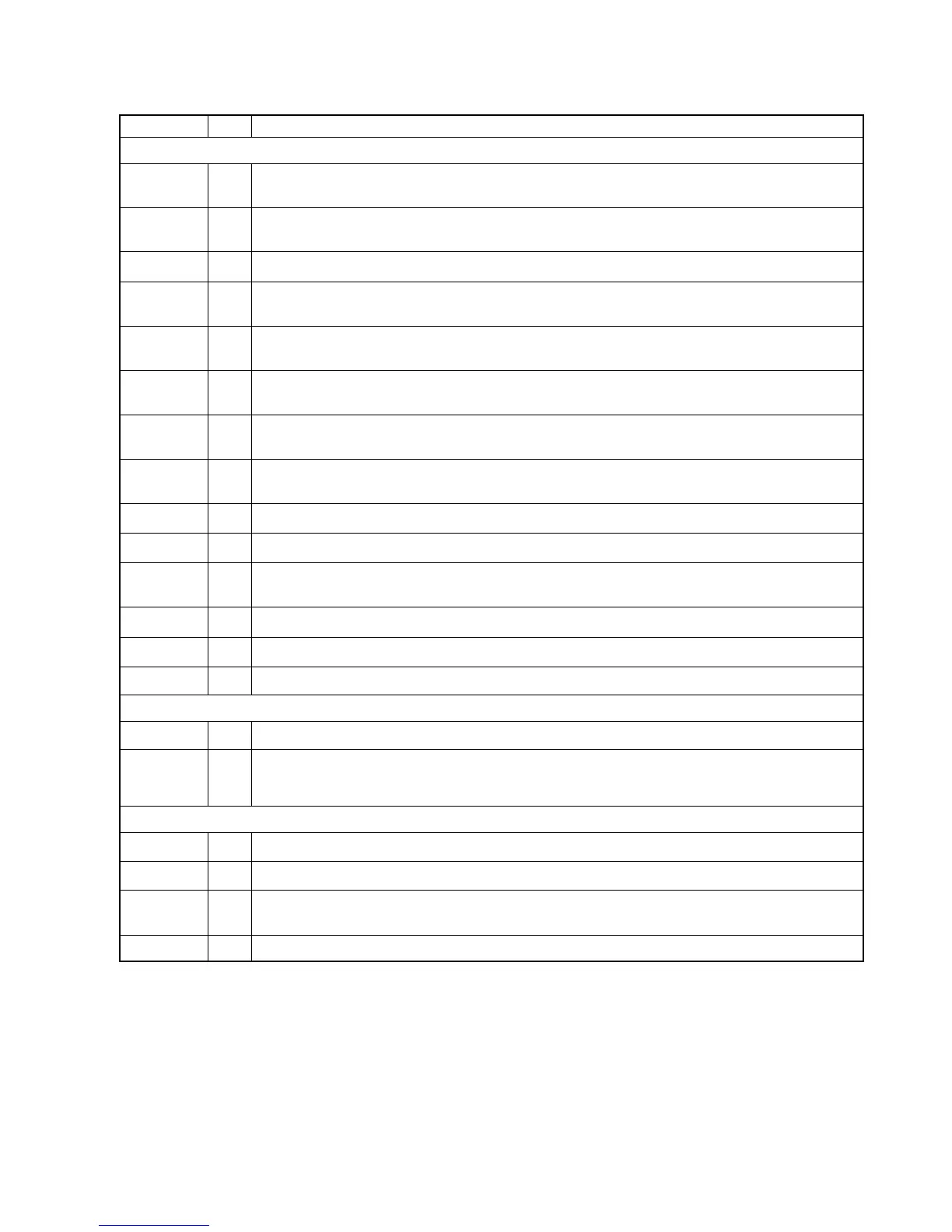

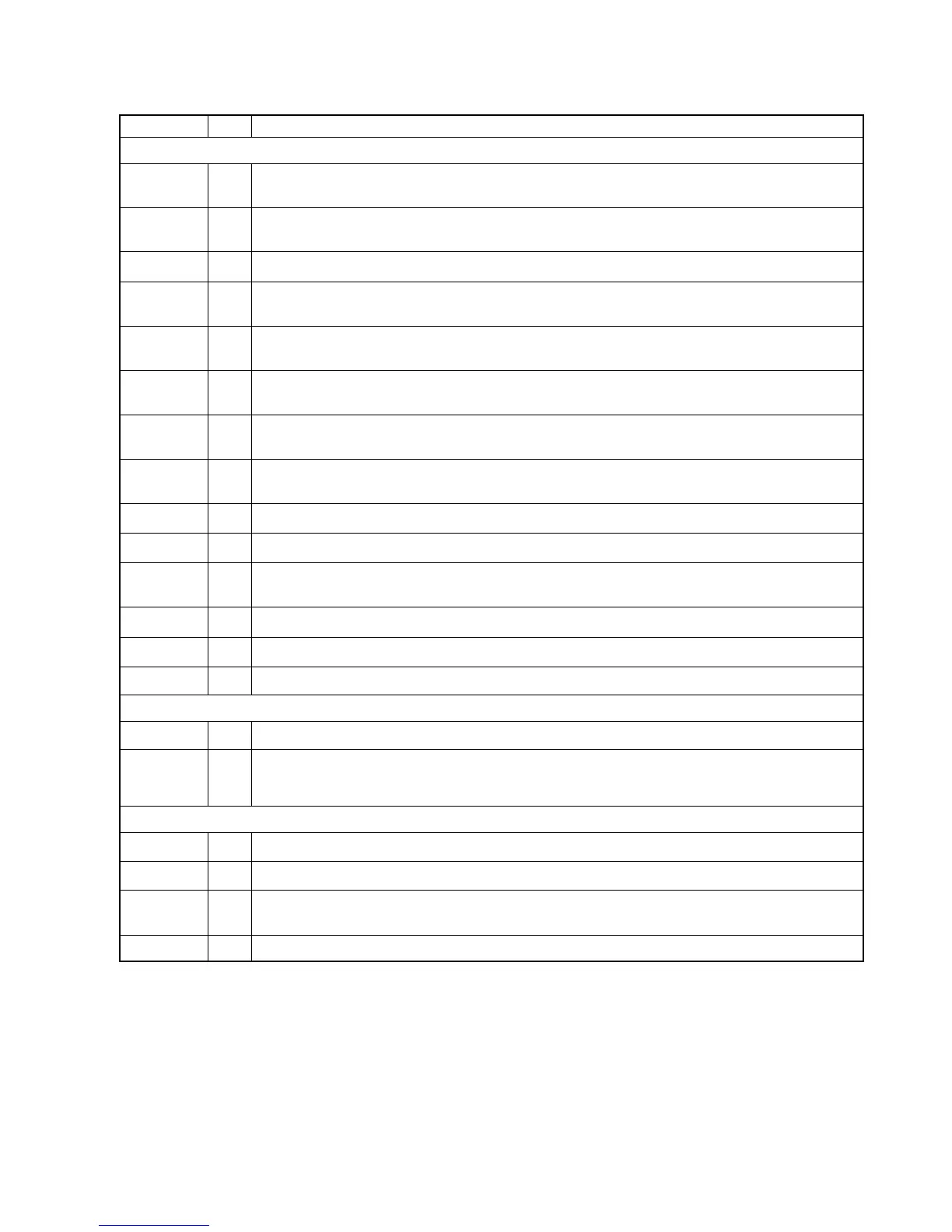

PIN NAME I/O DESCRIPTION

AD [31:0]

C/

~BE [3:0]

PAR

~FRAME

~TRDY

~IRDY

~STOP

~DEVSEL

IDSEL

CLK

~RST

~REQ

~GNT

~INTA

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

O

I

O

PCI multiplexed Address and Data Bus. A bus transaction consists of an address cycle followed by one or

more data cycles.

PCI Bus Command and Byte Enables. These signals carry the bus command during the address cycle and

byte enable during data cycles.

Parity. LynxEM+ asserts this signal to verify even parity across AD [31:0] and C/~BE [3:0].

Cycle Frame. LynxEM+ asserts this signal to indicate the beginning and duration of a bus transaction. It is

de-asserted during the final data cycle of a bus transaction.

Target Ready. A bus data cycle is completed when both ~IRDY and ~TRDY are asserted on the same

cycle.

Initiator Ready. A bus data cycle is completed when both ~IRDY and ~TRDY are asserted on the same

cycle.

Stop. LynxEM+ asserts this signal to indicate that the current target is requesting the master to stop current

transaction.

Device Select. LynxEM+ asserts this signal when it decodes its addresses as the target of the current

transaction.

ID Select. This input is used during PCI configuration read/write cycles.

PCI System Clock, 33 MHz.

PCI System Reset. LynxEM+ asserts this signal to force registers and state machines to initial default

values

PCI Bus Request (bus master mode)

PCI Bus Grant (bus master mode)

PCI Interrupt

Host Interface

Power Down Interface

~PDOWN

~CLKRUN/

ACTIVITY

I

O

Power down mode enable

~CLKRUN or LynxEM+ Memory and I/O activity detection depending on SCR18 [7]

0 = select ~CLKRUN

1 = select ACTIVITY

Clock Interface

REFCLK

CKIN

MCKIN/

LVDSCLK

~EXCKEN

I

I

I/O

I

32 KHz refresh clock source for power down or PALCLK for PALTV

14.318 MHz clock (~EXCKEN = 1) or Video Clock (~EXCKEN = 0)

Memory Clock In (~EXCKEN = 0) or LVDSCLK Out (~ESCKEN = 1), LVDSCLK is a free running clock

which can be used to drive LVDS transmitter for DSTN panels.

External Clock Enable. Select external VCLK form CKIN and MCLK from MCKIN.

8-12-2. Pin Function

Loading...

Loading...