TOTAL- ACEXTREME® SIGNALS

Data Device Corporation DS-BU-67301B-G

www.ddc-web.com

1/14

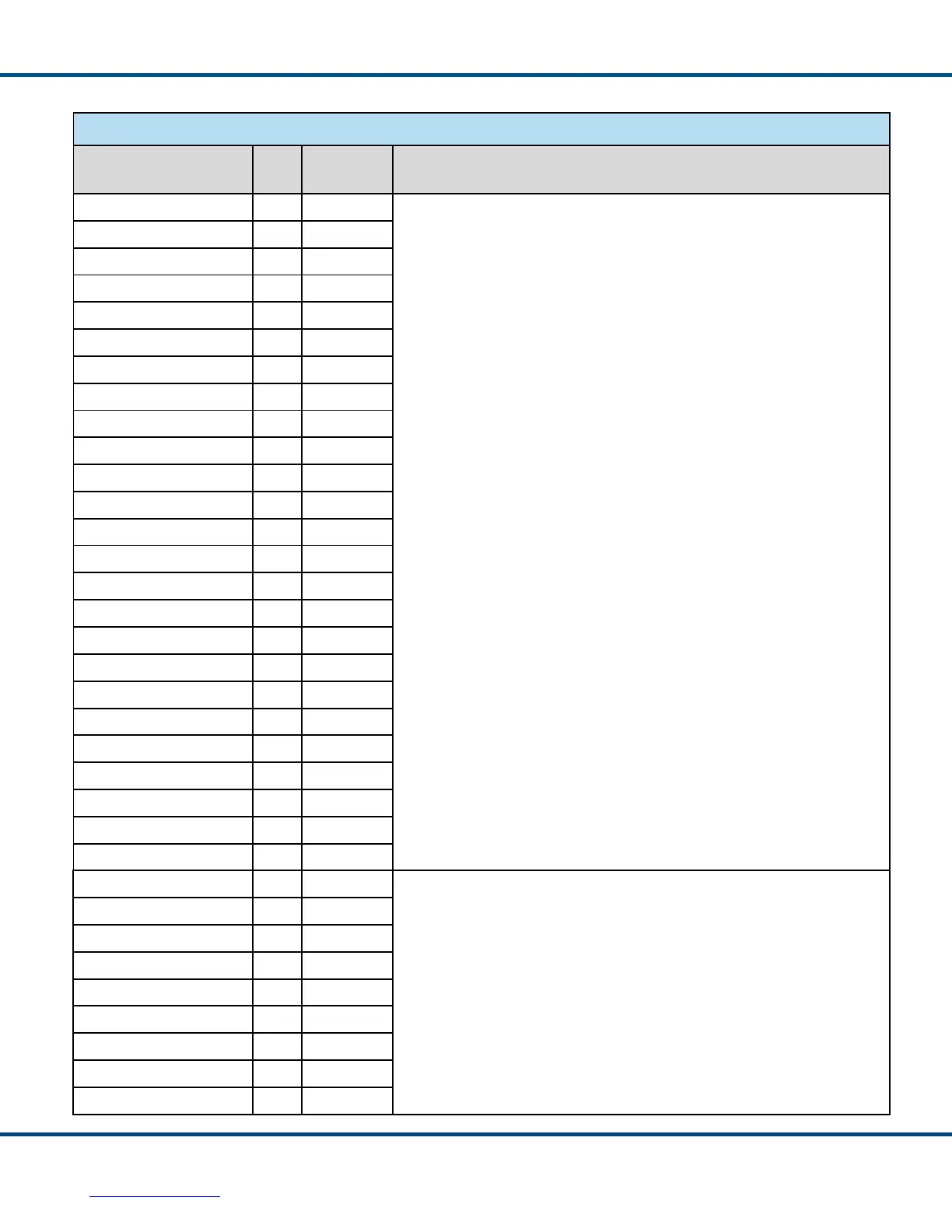

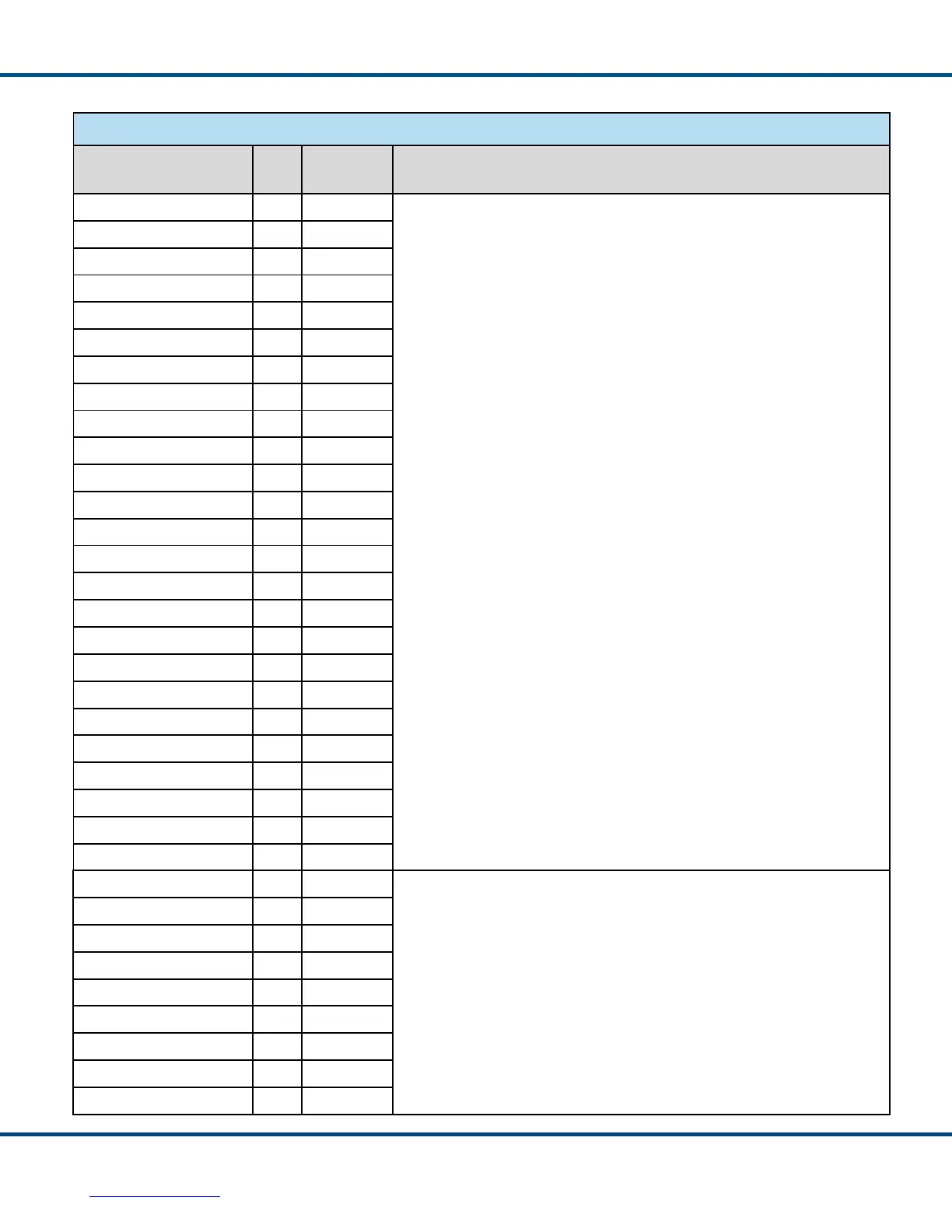

Table 19. CPU Data Bus

Signal Name BAL

L

Pullup/

Pulldown

Description

CPU_DATA(24) (I/O) D3 None

CPU_DATA(23) (I/O) F1 None

CPU_DATA(22) (I/O) E2 None

CPU_DATA(21) (I/O) E3 None

CPU_DATA(20) (I/O) F3 None

CPU_DATA(19) (I/O) G1 None

CPU_DATA(18) (I/O) G3 None

CPU_DATA(17) (I/O) J5 None

CPU_DATA(16) (I/O) H1 None

CPU_DATA(15) (I/O) K1 None

CPU_DATA(14) (I/O) M2 None

CPU_DATA(13) (I/O) L1 None

CPU_DATA(12) (I/O) N1 None

CPU_DATA(11) (I/O) L3 None

CPU_DATA(10) (I/O) K2 None

CPU_DATA(09) (I/O) M1 None

CPU_DATA(08) (I/O) N2 None

CPU_DATA(07) (I/O) N3 None

CPU_DATA(06) (I/O) N4 None

CPU_DATA(05) (I/O) M4 None

CPU_DATA(04) (I/O) K3 None

CPU_DATA(03) (I/O) M5 None

CPU_DATA(02) (I/O) L4 None

CPU_DATA(01) (I/O) K4 None

CPU_DATA(00) (I/O) L5 None

CPU_ADDR(15) (I) MSB T4 50k Pullup

16-bit CPU address bus.

The host CPU accesses Total-AceXtreme registers and internal RAM by

means of CPU_ADDR(15:0)

In the multiplexed address/data mode for the parallel CPU interface,

CPU_ADDR(15:0) may be left unconnected.

CPU_ADDR(14) (I) T3 50k Pullup

CPU_ADDR(13) (I) A6 None

CPU_ADDR(12) (I) B7 None

CPU_ADDR(11) (I) G2 None

CPU_ADDR(10) (I) D2 None

CPU_ADDR(09) (I) J1 None

CPU_ADDR(08) (I) H2 None

CPU_ADDR(07) (I) C3 None

Loading...

Loading...