HOST INTERFACE

Data Device Corporation DS-BU-67301B-G

www.ddc-web.com

1/14

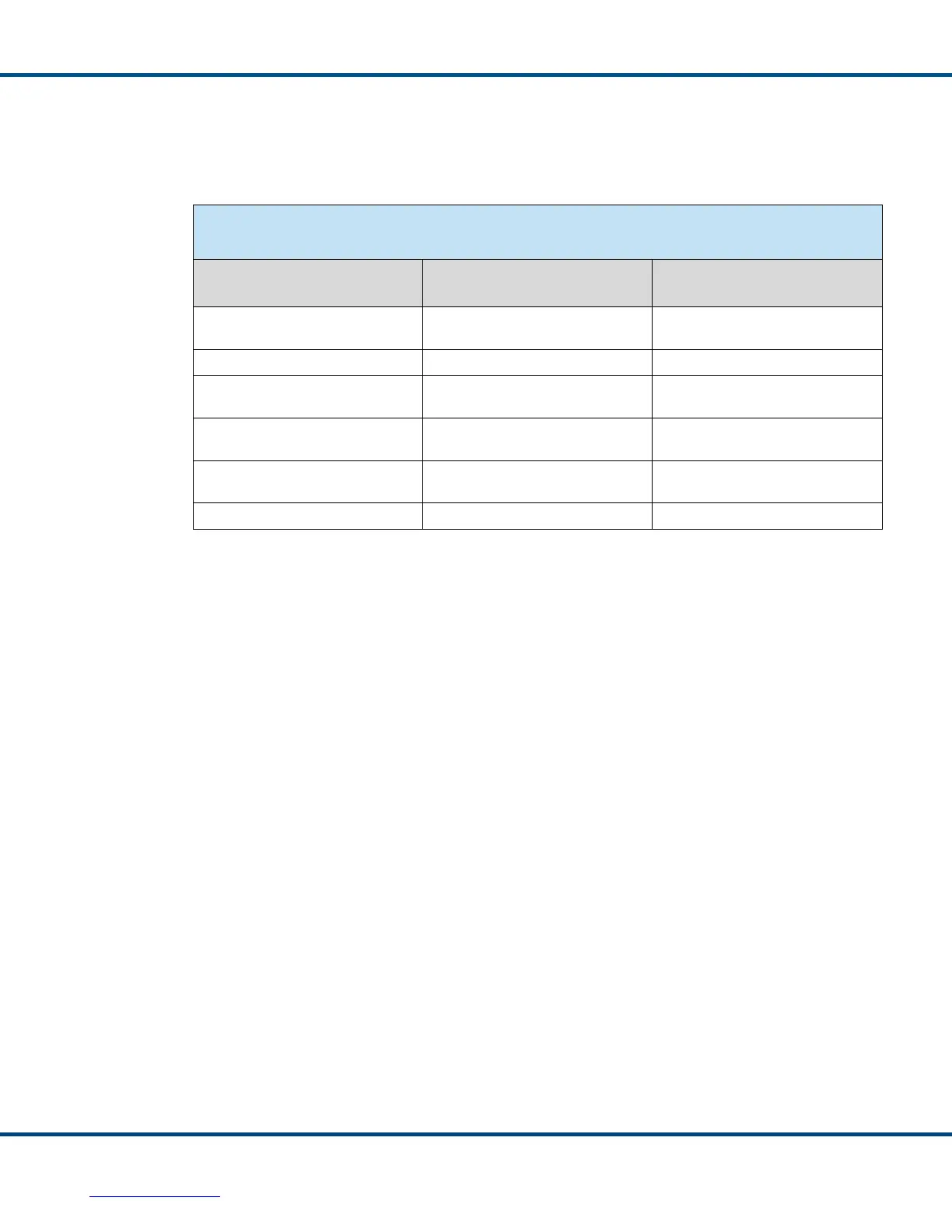

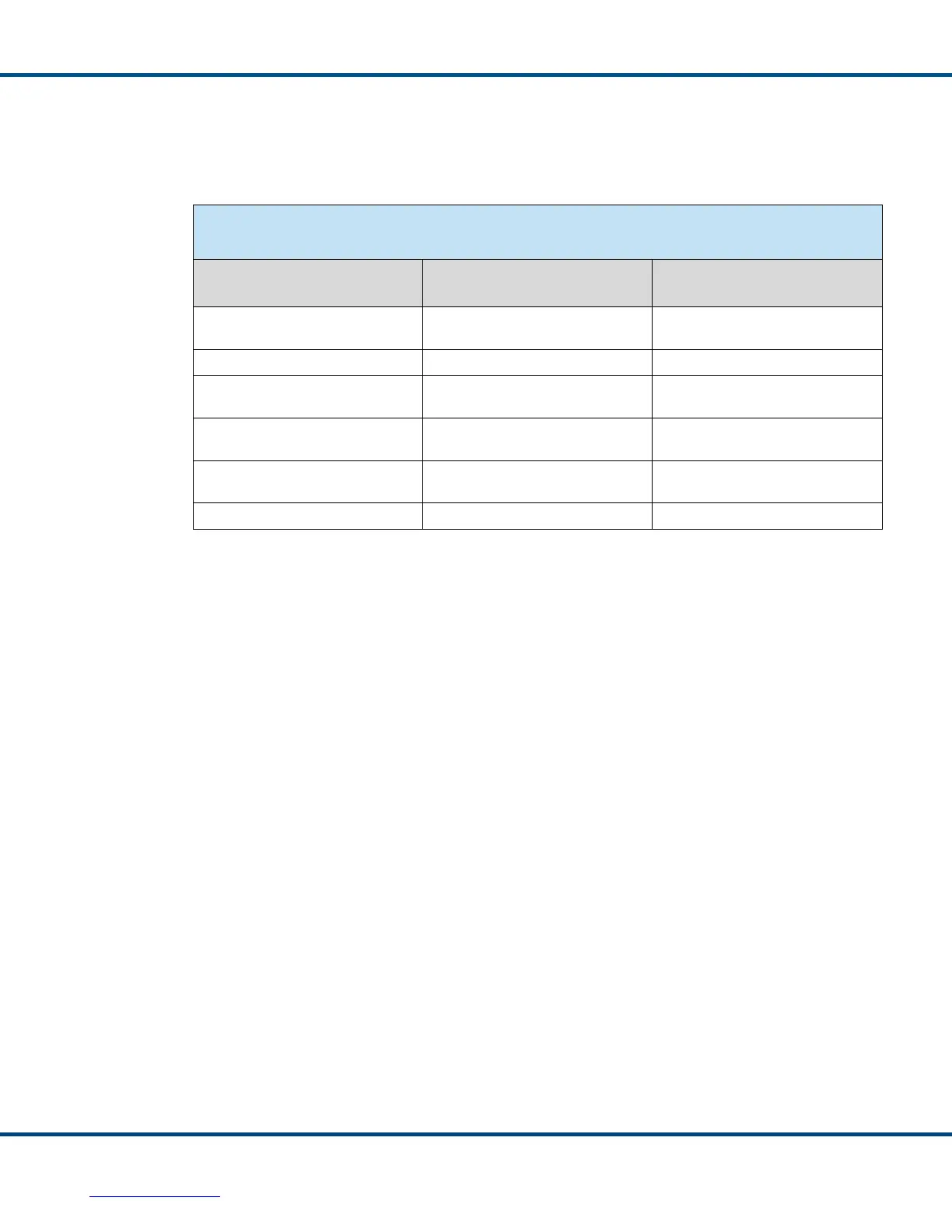

The operation of the nDATA_RDY signal for single-word Synchronous memory

and register accesses is summarized in Table 4 and described in the paragraphs

that follow.

Table 4. Summary of the Operation of the nDATA_RDY Output Signal for

Synchronous Single-Word Memory and Register Accesses

Transfer Type

Operation of nDATA_RDY

for Memory Access

Operation of nDATA_RDY

for Register Access

32-bit Read

Asserts low until host clock

following nSELECT going high

Asserts low for single clock cycle

32-bit Write Asserts low for single clock cycle Asserts low for single clock cycle

16-bit Read: First Word

Asserts low until host clock

following nSELECT going high

Asserts low for single clock cycle

16-bit Read: Second Word

Asserts low until host clock

following nSELECT going high

Asserts low for single clock cycle

16-bit Write: First Word Asserts low for single clock cycle

Asserts low until host clock

following nSELECT going high.

16-bit Write: Second Word Asserts low for single clock cycle Asserts low for single clock cycle

For 32-bit Synchronous single-word memory read accesses, nDATA_RDY

asserts low when the Total-AceXtreme® drives valid data to be read on

CPU_DATA(31:0), and de-asserts high on the HOST_CLK rising edge after

nSELECT is sampled high.

For Synchronous 32-bit single-word memory or register write accesses,

nDATA_RDY asserts low for a single host clock cycle when the data from

CPU_DATA(31:0) has been internally latched.

For Synchronous single-word register read accesses, nDATA_RDY asserts low

for a single host clock cycle beginning when the Total-AceXtreme® drives valid

data to be read on CPU_DATA(31:0) for a 32-bit transfer, or CPU_DATA(15:0)

for each of the two 16-bit transfers.

For each of the two transfers for 16-bit Synchronous single-word memory read

accesses, nDATA_RDY asserts low starting when the Total-AceXtreme® drives

valid data to be read on CPU_DATA(15:0) and de-asserts high on the

HOST_CLK rising edge after nSELECT is sampled high.

For each of the two transfers for 16-bit Synchronous single-word memory write

accesses, nDATA_RDY asserts low for a single host clock cycle when the Total-

AceXtreme® internally latches the data transferred over CPU_DATA(15:0).

Loading...

Loading...