HOST INTERFACE

Data Device Corporation DS-BU-67301B-G

www.ddc-web.com

1/14

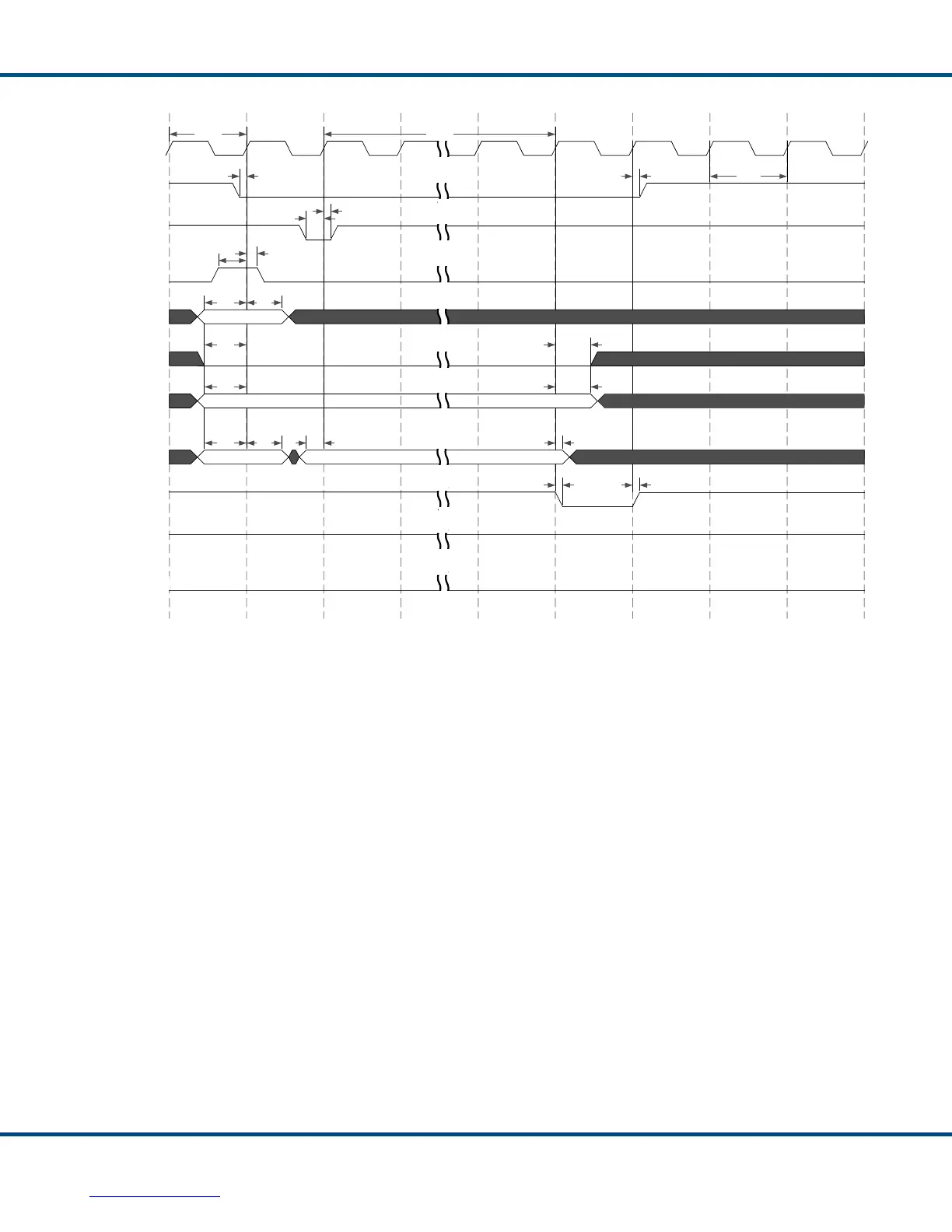

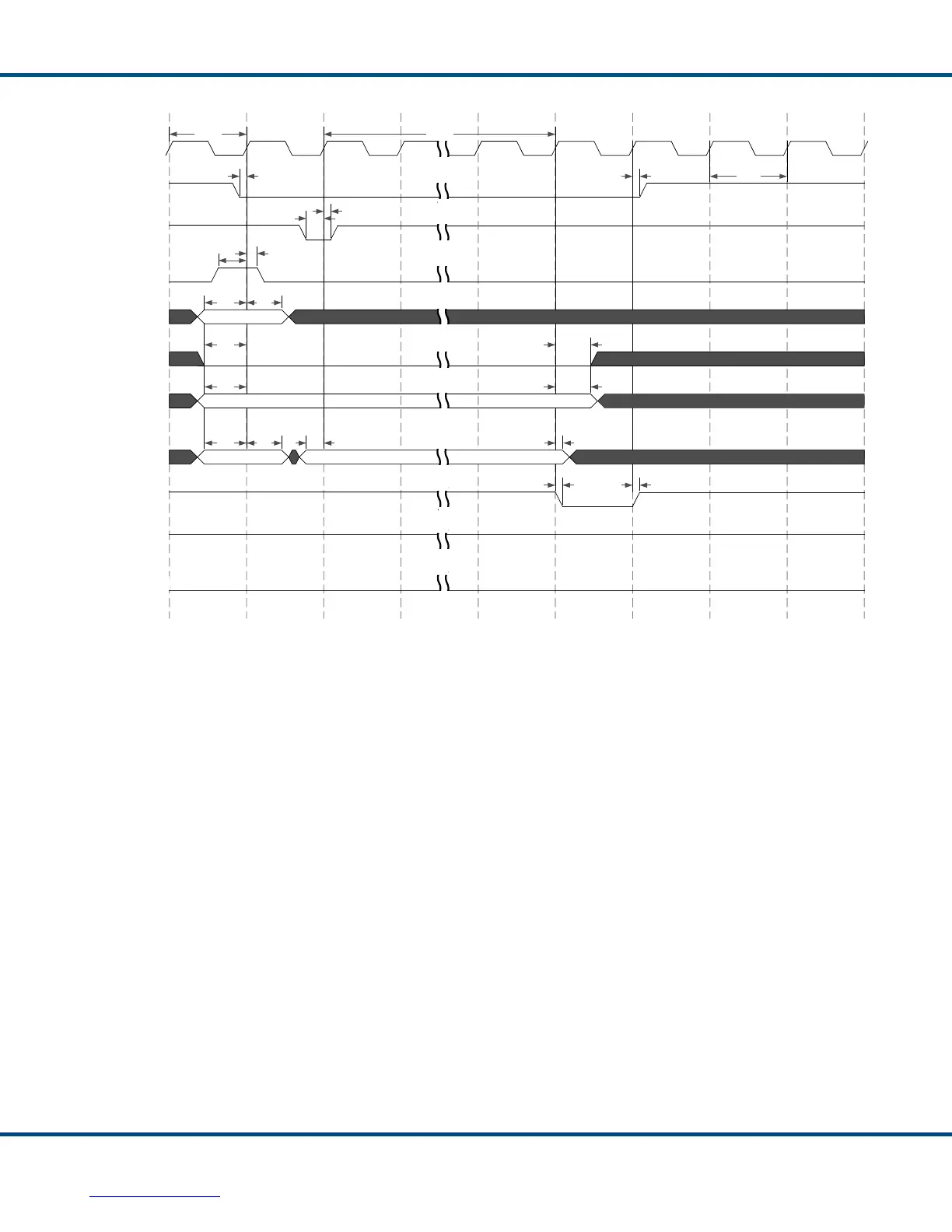

Figure 32. Synchronous, Multiplexed Address 32-bit Single-Word Write Timing

Figure 32 Notes:

1. When nSELECT is asserted (low), the Total-AceXtreme® is selected for this

data transfer. nSELECT must be asserted through the full transfer cycle, and

de-asserted high at the end of the transfer.

2. The CPU_WORD_EN[1:0] inputs are used to specify which 16-bit data

memory word(s) are to be written. If either or both these bits is ‘0’, then the

corresponding 16-bit word(s) will not be written. These inputs should be tied

high if unused. For register transfers, the value of CPU_WORD_EN[1:0] must

be ‘11’.

3. Unless the Total-AceXtreme command FIFO is full, CPU_nSTOP is not

asserted for write accesses, and will remain high.

CPU_nSTOP

nDATA_RDY

CPU_DATA

CPU_WORD_EN[1:0]

RD_nWR

MEM_nREG

ADDR_LAT

nDATA_STRB

nSELECT

HOST_CLK

tAH

tAH

tDS

tCLK

tRDD tRDD

tAS

tAH

tALS

tALH

tCS

tSH

tSS

tCH

DataAddress

tAS

tAS

tAS

tAH

tWait

tSHC

tDS

CPU_nLAST

Loading...

Loading...