EDGECORE NETWORKS CORPORATION 2018

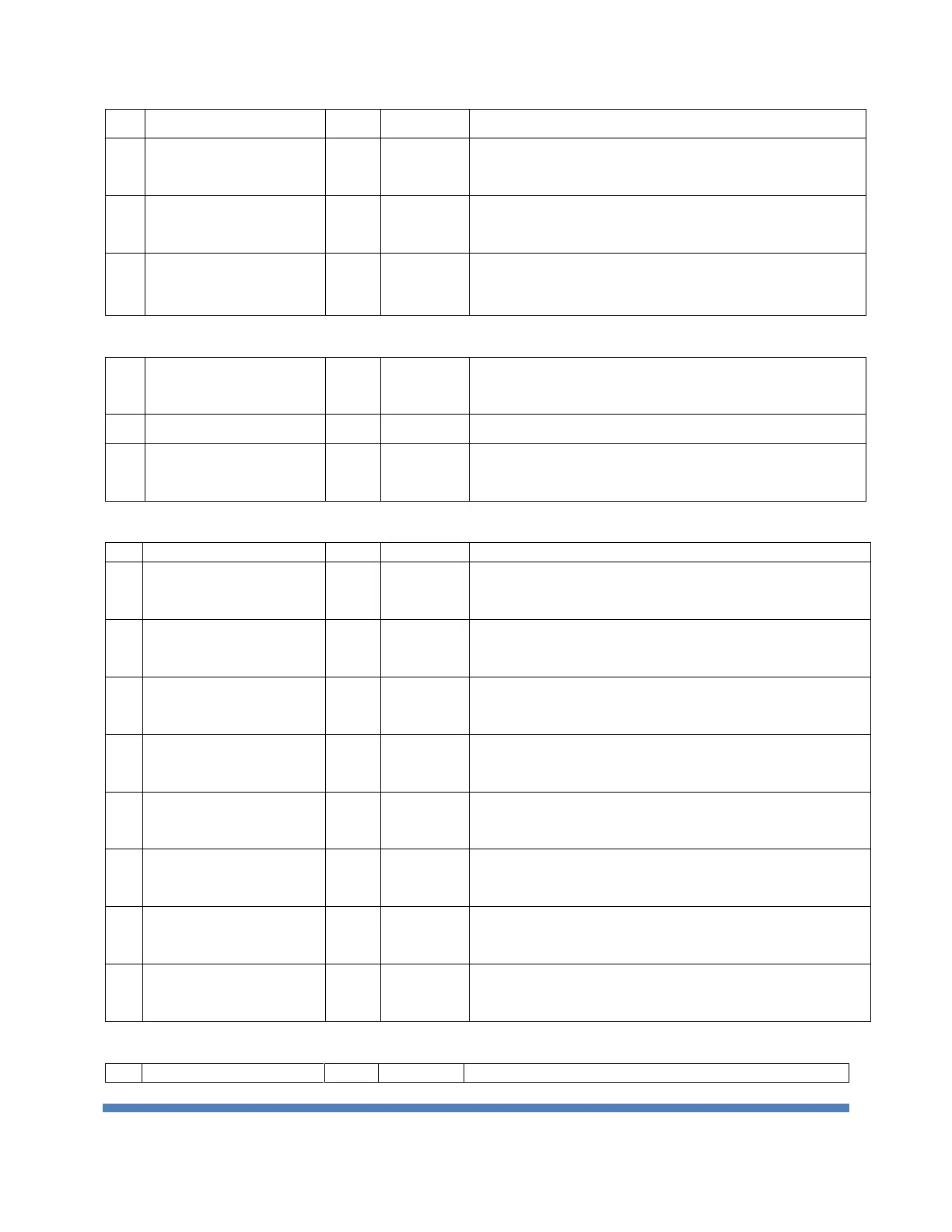

0: CPU_JTAG_RST is placed in reset state.

1: RESET_SYS_CPLD is placed in normal operation state.

0: RESET_SYS_CPLD is placed in reset state.

1: Non-push the push button of front panel

0: Push the push button of front panel

1: POWER_RST is placed in normal operation state.

0: POWER_RST is placed in reset state.

5.12.2.10. Offset 0x09 System Reset-6 (Read& Write)

System Reset Lock

(RESET_MAC)

1: Lock system reset signal to be high.

0: System reset signal to be normal. (Default)

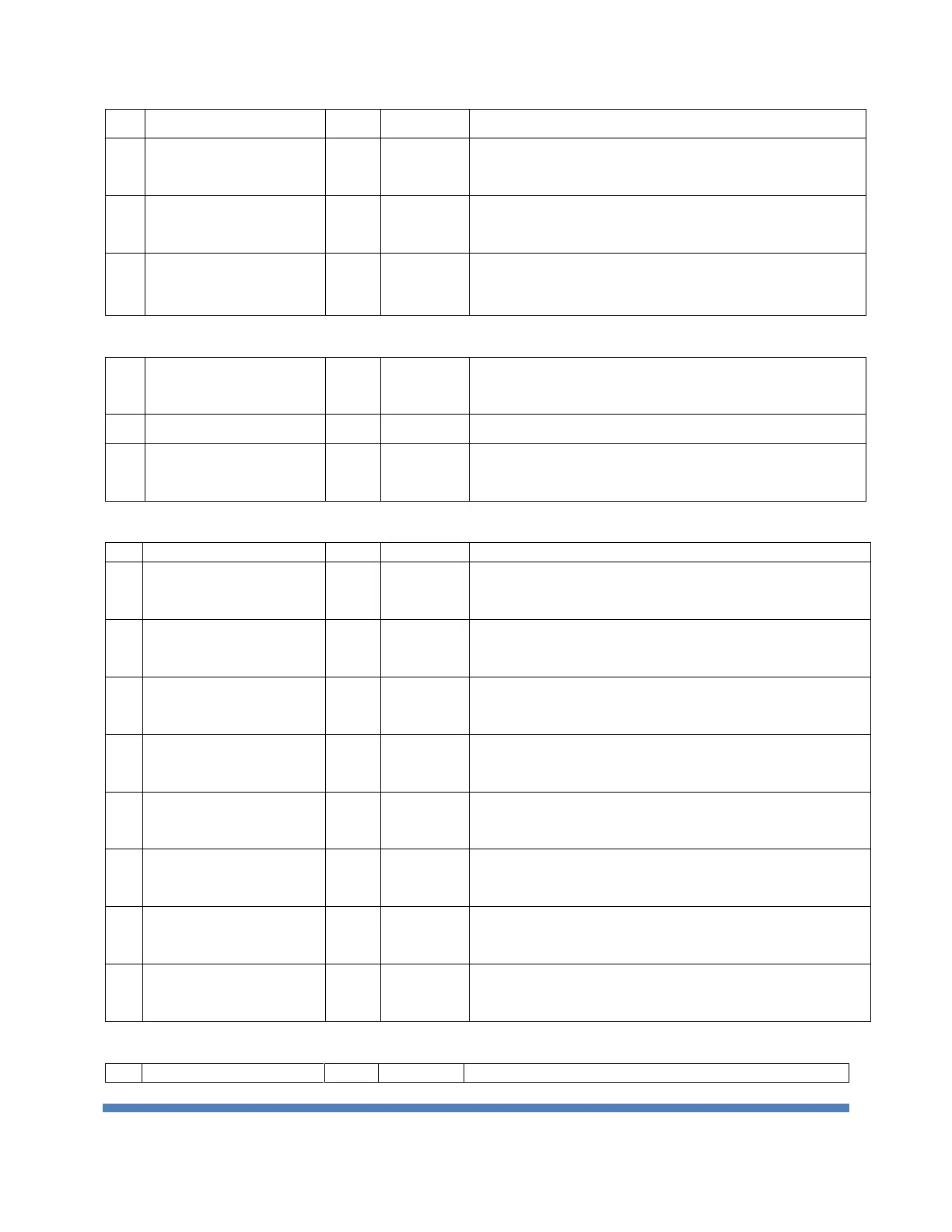

5.12.2.11. Offset 0x0A Interrupt Status-1 (Read Only)

INTB* P56 QSFP28

(P56_INT)

1:No interrupt

0: There is INTR from QSFP28 transceiver Port 56

INTB* P55 QSFP28

(P55_INT)

1:No interrupt

0: There is INTR from QSFP28 transceiver Port 55

INTB* P54 QSFP28

(P54_INT)

1:No interrupt

0: There is INTR from QSFP28 transceiver Port 54

INTB* P53 QSFP28

(P53_INT)

1:No interrupt

0: There is INTR from QSFP28 transceiver Port 53

INTB* P52 QSFP28

(P52_INT)

1:No interrupt

0: There is INTR from QSFP28 transceiver Port 52

INTB* P51 QSFP28

(P51_INT)

1:No interrupt

0: There is INTR from QSFP28 transceiver Port 51

INTB* P50 QSFP28

(P50_INT)

1:No interrupt

0: There is INTR from QSFP28 transceiver Port 50

INTB* P49 QSFP28

(P49_INT)

1:No interrupt

0: There is INTR from QSFP28 transceiver Port 49

5.12.2.12. Offset 0x0B Interrupt Status-2 (Read Only)

Loading...

Loading...