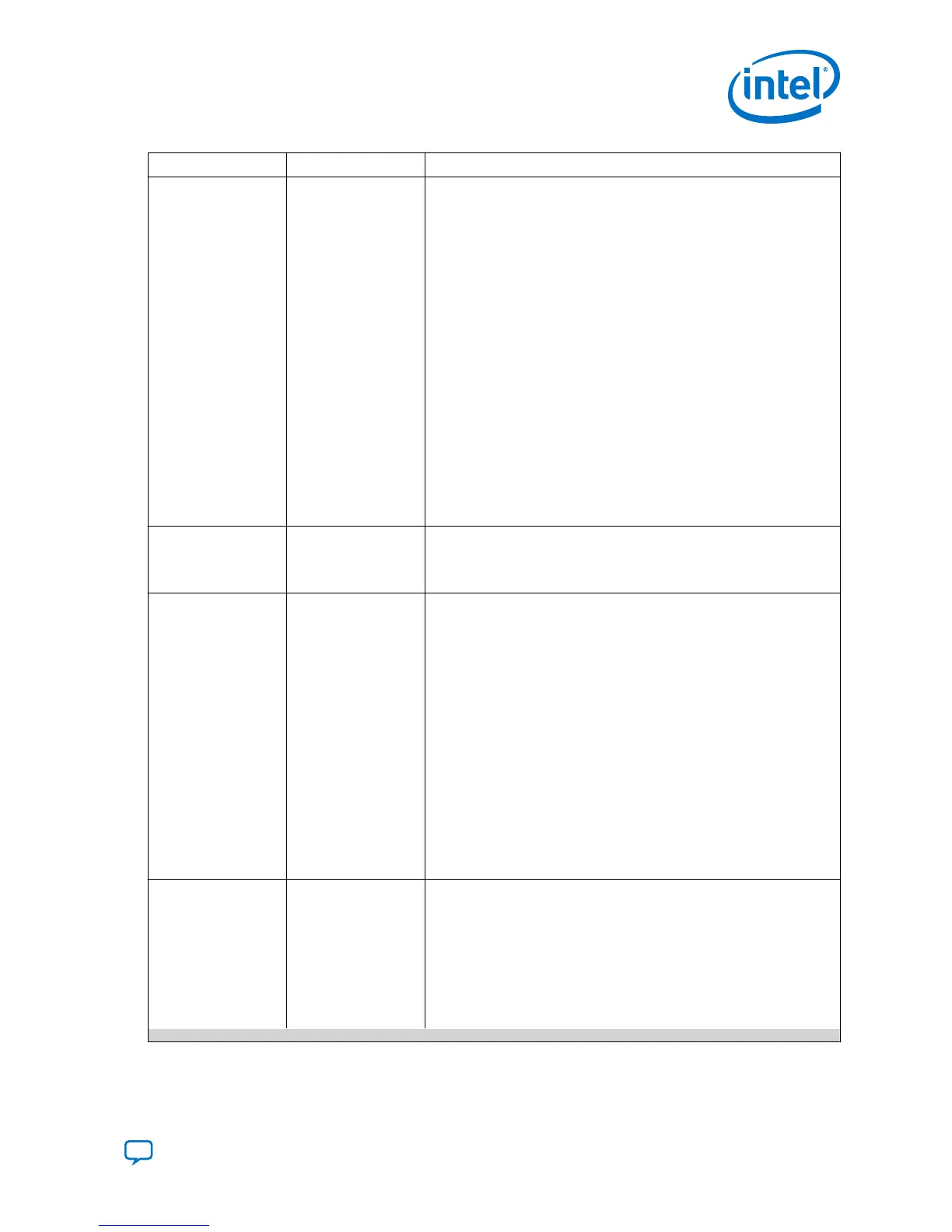

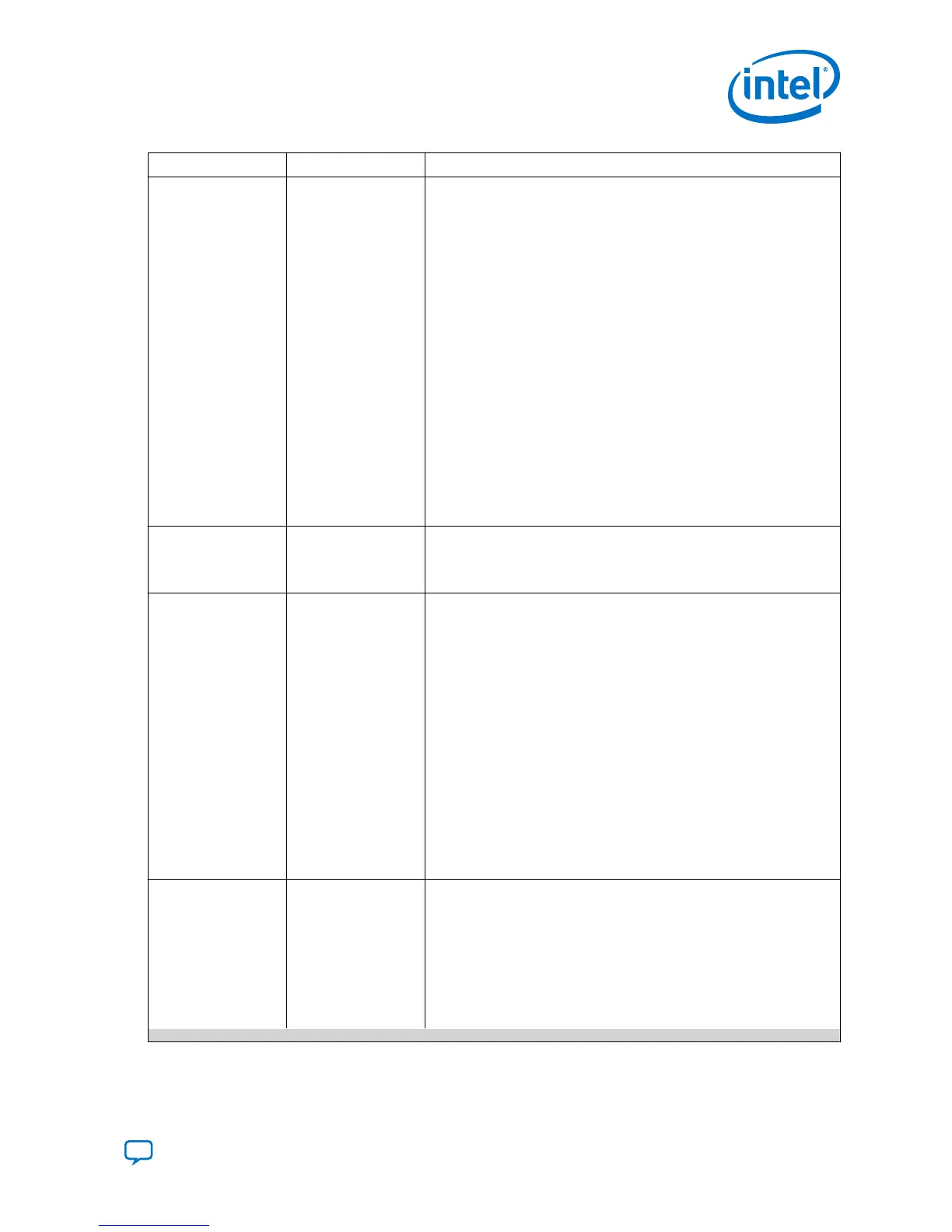

Date Version Changes

• Added Configuration Pins I/O Standard and Drive Strength table.

• Updated information about maximum additional data words when

using 2-stage register synchronizer.

• Updated the equation for minimum AS configuration time estimation.

• Added RBF Configuration File Format section explaining the format of

the .rbf file.

• Updated Configuration Sequence to state that a firmware which is

part of the configuration data if loaded in the device initially.

• Updated description for Number of flash devices used parameter

in the PFL II Flash Interface Setting Parameters table.

• Updated Configuration via Protocol overview and added link to the

Configuration via Protocol (CvP) Implementation User Guide.

• Updated Partial Reconfiguration overview and added link to the

Creating a Partial Reconfiguration Design chapter of the Handbook

Volume 1: Design and Compilation.

• Updated Design Security Overview descriptions.

• Added note for Partial Reconfiguration feature and link to Partial

Reconfiguration Solutions IP User Guide in Intel Stratix 10

Configuration Overview.

• Removed SDM pin notes in Intel Stratix 10 Configuration Overview.

•

Updated internal oscillator's AS_CLK frequency in Supported

configuration clock source and AS_CLK Frequencies in Intel Stratix

10 Devices table.

May 2017 2017.05.22 • Updated Connection Setup for Programming the EPCQ-L Device using

the AS Interface figure.

• Updated guideline to program the EPCQ-L device in Programming

EPCQ-L Devices using the Active Serial Interface.

April 2017 2017.04.10 • Updated note for AS Fast Mode in MSEL Settings for Each

Configuration Scheme of Devices table.

• Added note to Configuration via Protocol recommending user to use

AS x4 fast mode for CvP application.

• Updated instances of Spansion to Cypress.

• Added note to Normal Mode in MSEL Settings for Each Configuration

Scheme of Devices table.

• Updated note and description in Configuration Overview.

• Removed AS x1 support.

• Added Connection Setup for SD/MMC Single-Device Configuration

figure.

• Updated Connections for AS x4 Single-Device Configuration,

Connection Setup for AS Configuration with Multiple EPCQ-L Devices,

Connection Setup for Programming the EPCQ-L Devices using the

JTAG Interface, Connection Setup for NAND Flash Single-Device

Configuration, and Connection Setup for SD/MMC Single-Device

Configuration to include note about nCONFIG test point.

•

Added note in Avalon-ST Configuration stating that AVST_CLK should

be continuous.

February 2017 2017.02.13 • Updated Configuring Stratix 10 Devices using AS Configuration

section and subsections to include .jic for AS configuration scheme.

• Added Programming .jic files into EPCQ-L Device.

• Updated the SDM description.

• Updated SDM block diagram by adding Mailbox block and note for

Avalon-ST x8 configuration scheme.

• Updated Configuration Sequence Diagram.

• Updated configuration sequence descriptions.

• Updated Avalon-ST Bus Timing Waveform figure.

continued...

8. Document Revision History for the Intel Stratix 10 Configuration User Guide

UG-S10CONFIG | 2018.11.02

Send Feedback

Intel Stratix 10 Configuration User Guide

109

Loading...

Loading...