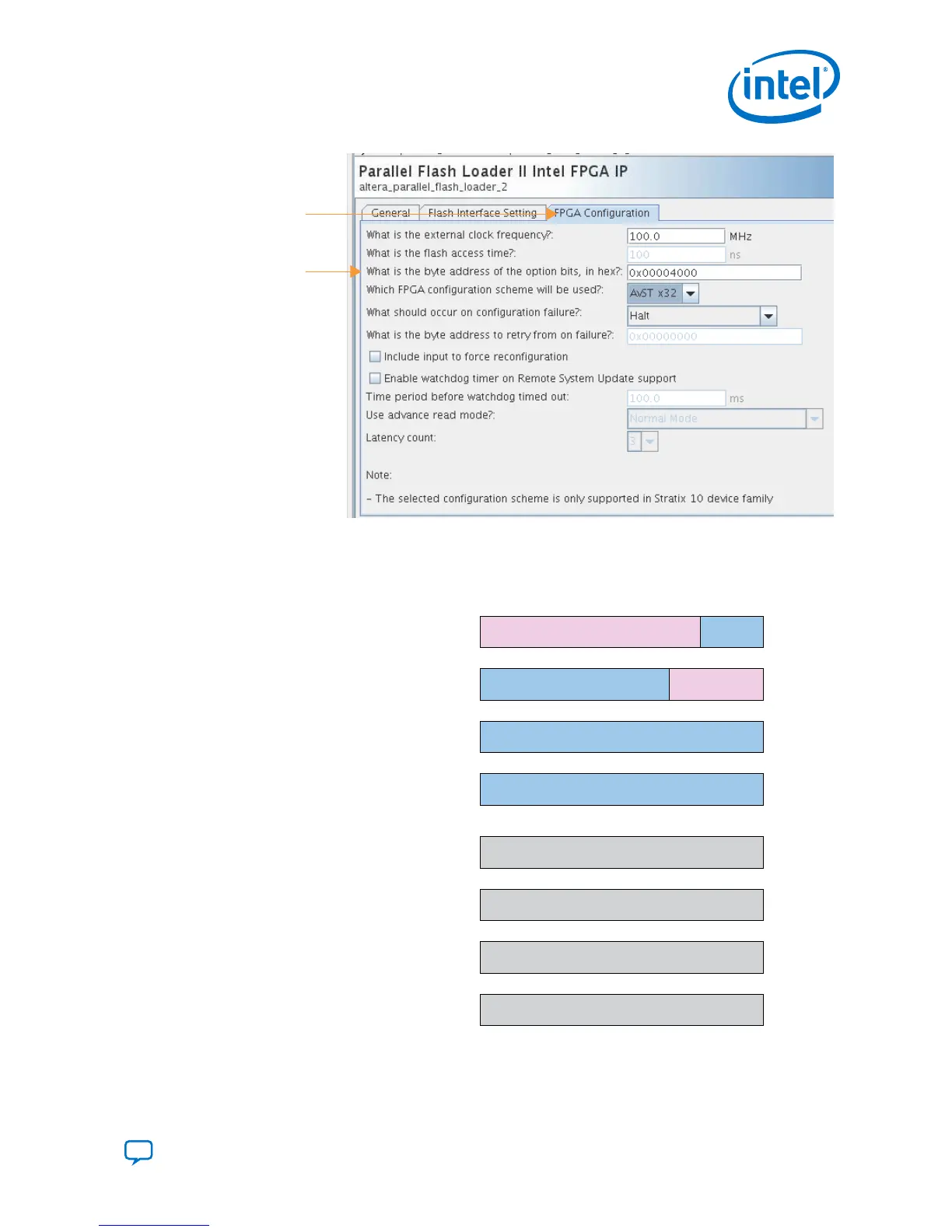

Option bits

FPGA Configuration

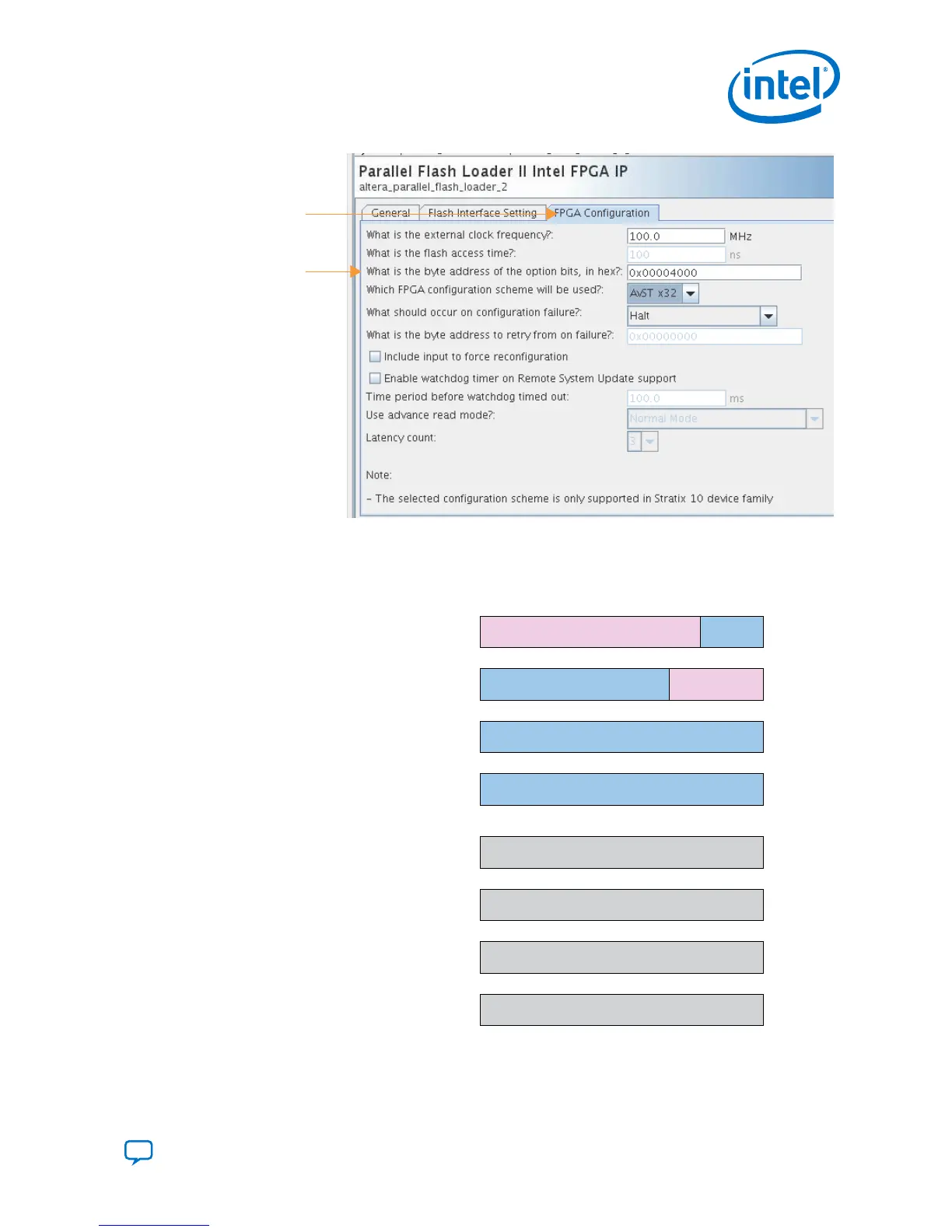

Figure 19. Page Start Address, End Address, and Page-Valid Bit Stored as Option Bits

Bits 0 to 12 for the page start address are set to zero and are not stored as option bits. The Page-Valid bits

indicate whether each page is successfully programmed. The PFL II IP core programs the Page-Valid bits after

successfully programming the pages.

Bit 2...Bit 0Bit 7...Bit 3

Bit 7...Bit 0

Bit 7...Bit 0

Bit 7...Bit 0

Bit 7...Bit 0

Bit 7...Bit 0

Bit 7...Bit 0

Bit 7...Bit 1 Bit 0

0x002002

0x002003

0x002000

0x002001 Page Start Address [17:13]

Page Start Address [25:18]

Page Start Address [33:26]

Page End Address [9:2]

Page End Address [17:10]

Page End Address [25:18]

0x002004

0x002005

0x002006

Page End Address [33:26]

Page ValidReserved

Reserved

0x002007

(For flash byte addressing mode)

3. Intel Stratix 10 Configuration Schemes

UG-S10CONFIG | 2018.11.02

Send Feedback

Intel Stratix 10 Configuration User Guide

41

Loading...

Loading...