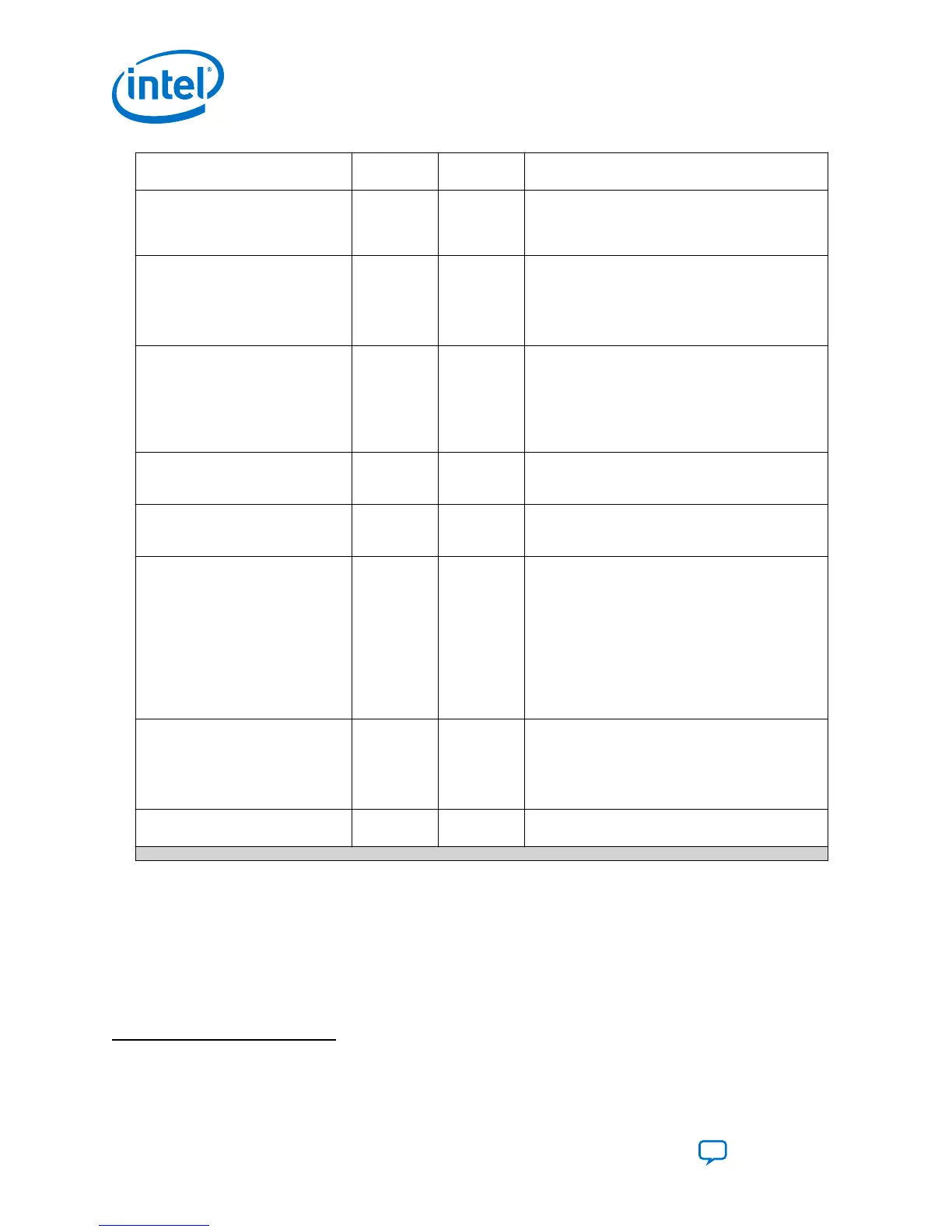

Pin Type Weak Pull-

Up

Function

flash_data bus. The output of this pin depends on

the setting of the unused pins if you did not select

the PFL II interface tri-state option when the PFL II

is not accessing the flash memory device.

flash_data[]

Input or

Output

(bidirectional

pin)

— Data bus to transmit or receive 8- or 16-bit data to

or from the flash memory in parallel. The output of

this pin depends on the setting of the unused pins if

you did not select the PFL II interface tri-state

option when the PFL II is not accessing the flash

memory device.

(12)

flash_nce[]

Output —

Connects to the nCE pin of the flash memory

device. A low signal enables the flash memory

device. Use this pin for multiple flash memory

device support. The flash_nce pin is connected to

each nCE pin of all the connected flash memory

devices. The width of this port depends on the

number of flash memory devices in the chain.

flash_nwe

Output —

Connects to the nWE pin of the flash memory

device. A low signal enables write operation to the

flash memory device.

flash_noe

Output —

Connects to the nOE pin of the flash memory

device. A low signal enables the outputs of the flash

memory device during a read operation.

flash_clk

Output —

Used for burst mode. Connects to the CLK input pin

of the flash memory device. The active edges of CLK

increment the flash memory device internal address

counter. The flash_clk frequency is half of the

pfl_clk frequency in burst mode for single CFI

flash. In dual P30 or P33 CFI flash solution, the

flash_clk frequency runs at a quarter of the

pfl_clk frequency. Use this pin for burst mode

only. Do not connect these pins from the flash

memory device to the host if you are not using

burst mode.

flash_nadv

Output — Used for burst mode. Connects to the address valid

input pin of the flash memory device. Use this signal

for latching the start address. Use this pin for burst

mode only. Do not connect these pins from the flash

memory device to the host if you are not using

burst mode.

flash_nreset

Output — Connects to the reset pin of the flash memory

device. A low signal resets the flash memory device.

continued...

(12)

Intel recommends not inserting logic between the PFL II pins and the host I/O pins, especially

on the flash_data and fpga_nconfig pins.

3. Intel Stratix 10 Configuration Schemes

UG-S10CONFIG | 2018.11.02

Intel Stratix 10 Configuration User Guide

Send Feedback

50

Loading...

Loading...