MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

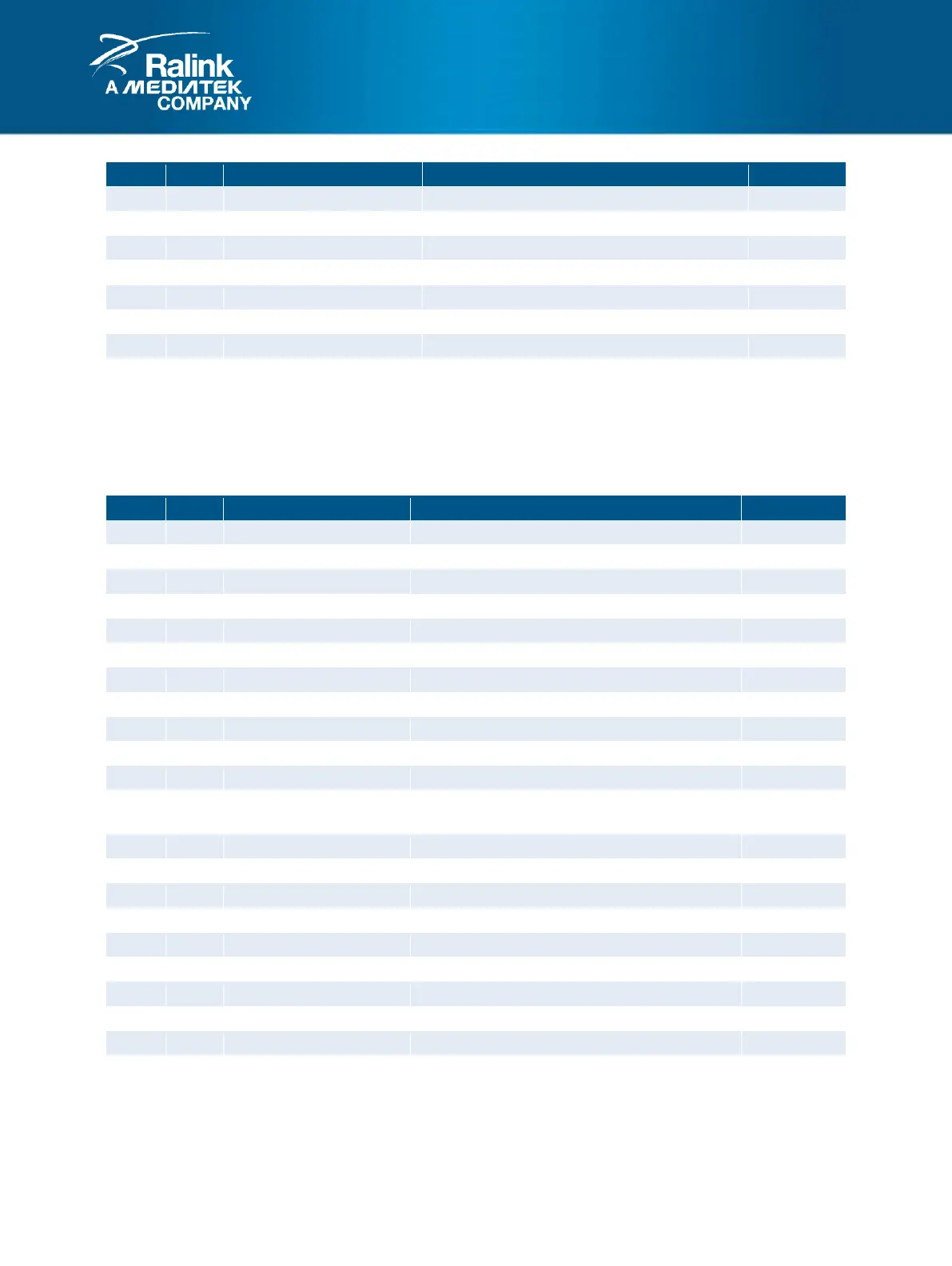

PIO interrupt status type

UART interrupt status type

PCM interrupt status type

Illegal access interrupt status type

Watchdog timer interrupt status type

Timer 0 interrupt status type

System control interrupt status type

NOTE:

0: IRQ type 0

1: IRQ type 1

The interrupt type may be changed at any time; if the interrupt type is changed while the interrupt is active,

the interrupt is immediately redirected.

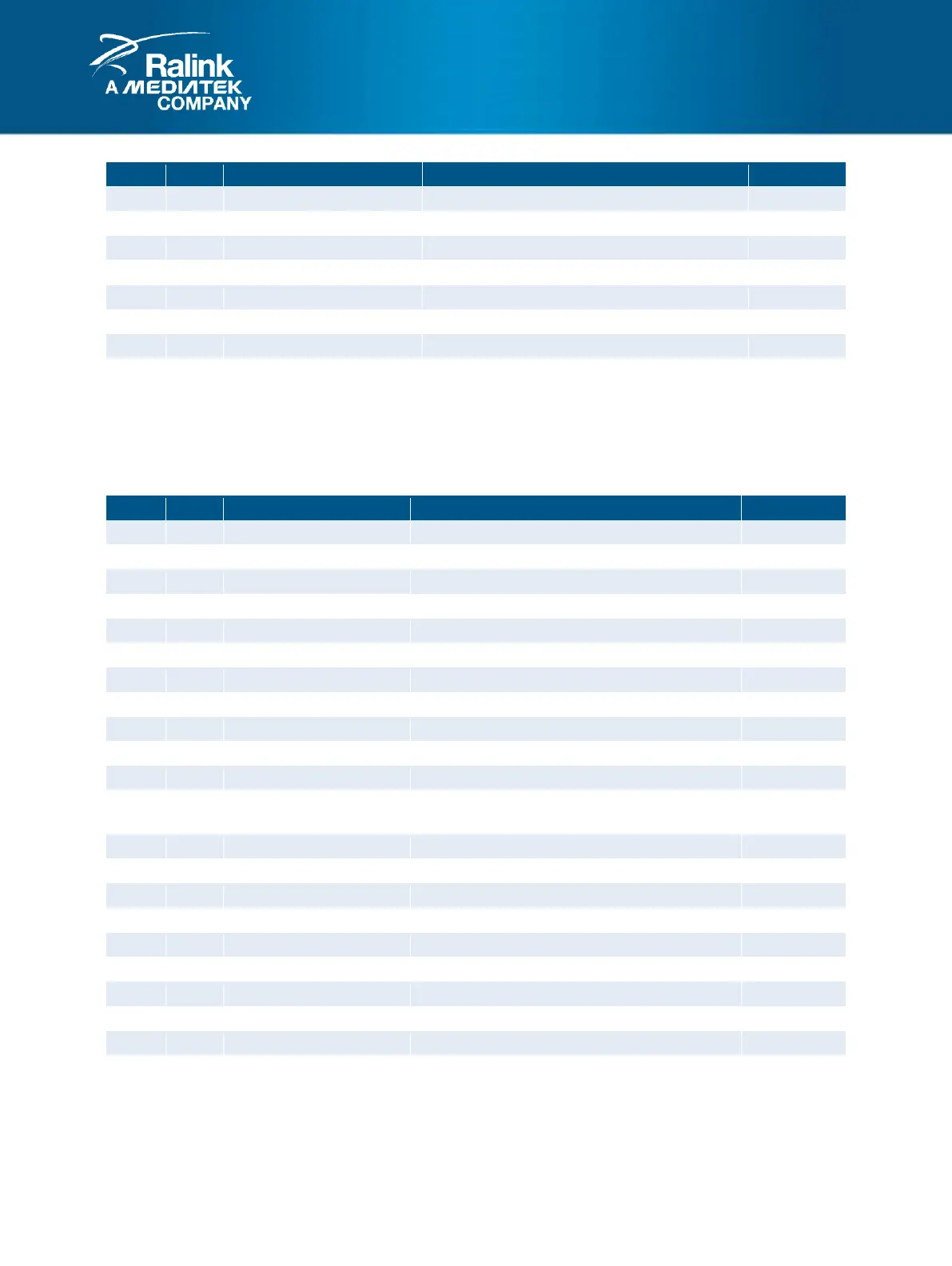

40. INTRAW: Raw Interrupt Status before Enable Mask (offset: 0x0030)

USB device interrupt status before mask

USB host interrupt status before mask

Ethernet Switch interrupt status before mask

R2P interrupt status before mask

SDHC interrupt status before mask

UARTLITE interrupt status before mask

SPI interrupt status before mask

I2S interrupt status before mask

MIPS performance counter interrupt status

before mask

DMA interrupt status before mask

PIO interrupt status before mask

UART interrupt status before mask

PCM interrupt status before mask

Illegal access interrupt status before mask

Watchdog timer interrupt status before mask

Timer 0 interrupt status before mask

System control interrupt status before mask

NOTE: These bits are set if the corresponding interrupt is asserted from the source. The status bit is set if the

interrupt is active, even if it is masked, and regardless of the interrupt type. This provides a single-access

snapshot of all active interrupts for implementation of a polling system.

Loading...

Loading...