2

PERFORMANCE SPECIFICATION

2

- 2

1

Overview

2

Performance

Specification

3

Sequence Program

Configuration and

Execution Conditions

4

I/O Nunber Assignment

5

Memories and Files

Handled by CPU Module

6

Functions

7

Communication with

Intelligent Function

Module

8

Parameters

.

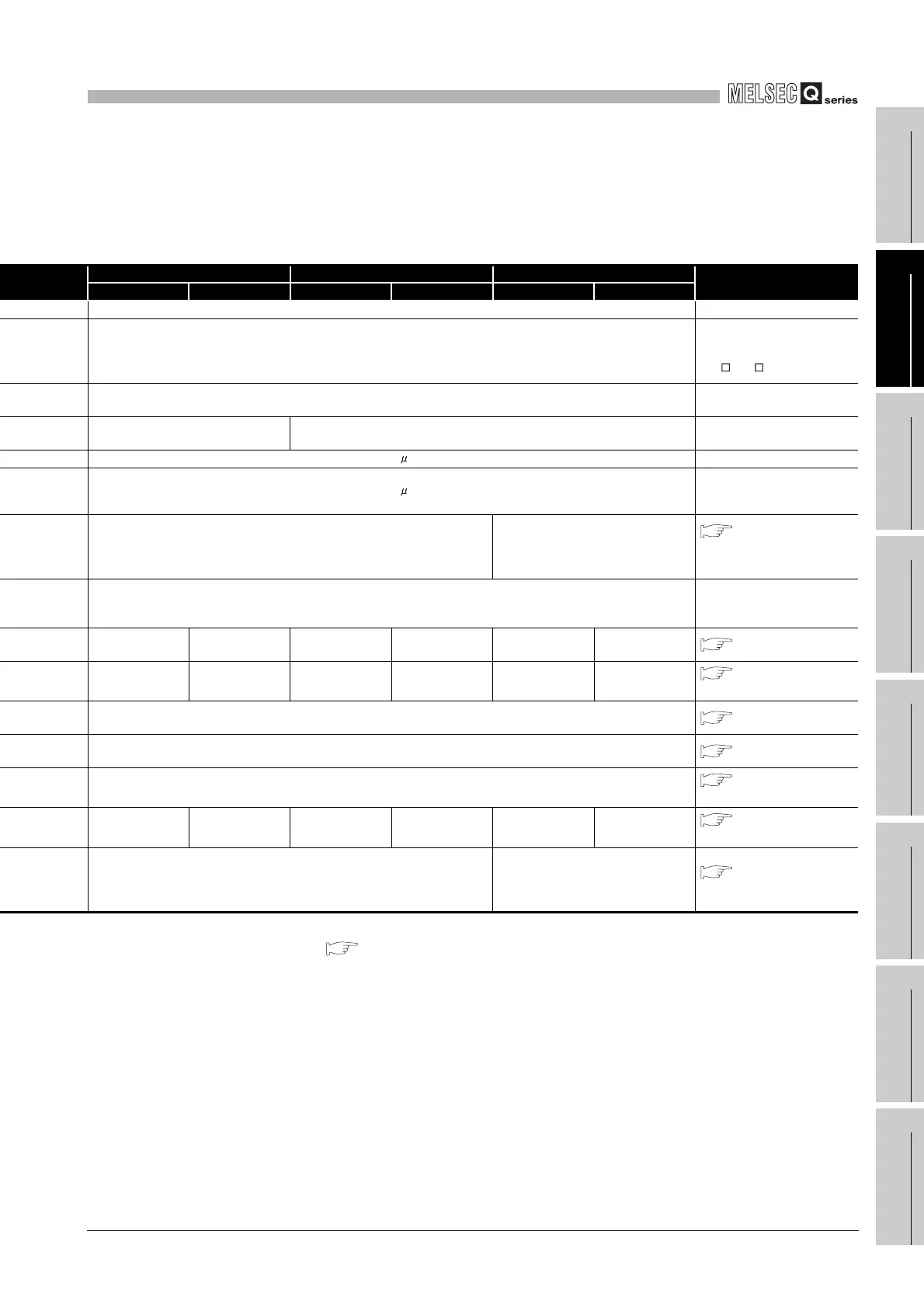

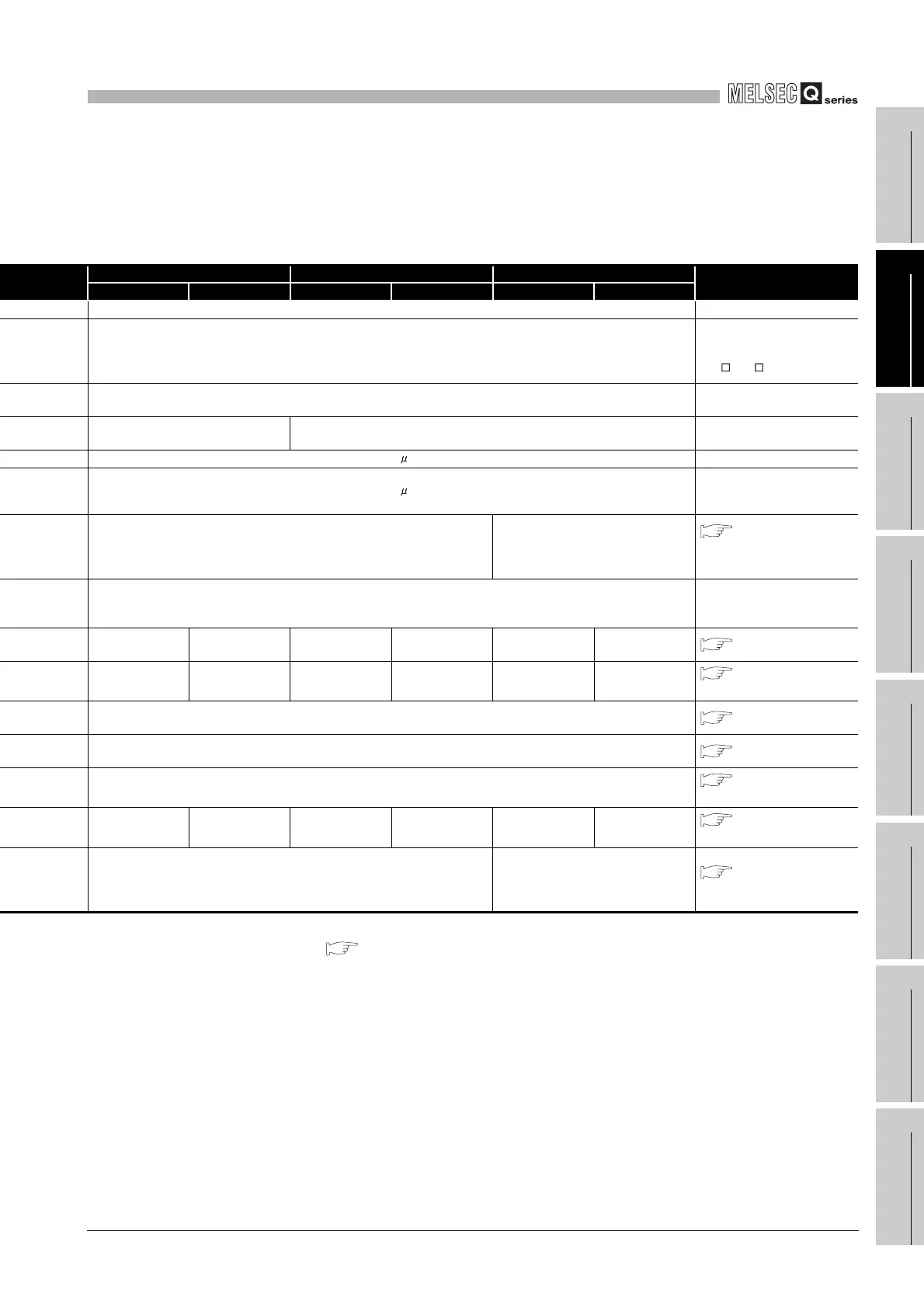

* 4 : The CPU shared memory is not latched.

QCPU User's Manual (Multiple CPU System)

The CPU shared memory is cleared when the power is turned on to the PLC or when the CPU

module is reset.

High Performance model QCPU Process CPU Redundant CPU

Remark

Q12HCPU Q25HCPU Q12PHCPU Q25PHCPU Q12PRHCPU Q25PRHCPU

Repetitive operation of stored program ----

Refresh mode

Direct I/O is possible by direct

I/O specification

(DX , DY )

Relay symbol language, logic symbolic language,MELSAP3 (SFC), MELSAP-L, Function block,

structured text (ST)

----

---- FBD for process control

Use PX Developer for

programming.

0.034 s ----

0.102 s ----

----

Device memory 48k word points: 22ms

Device memory 100k word points: 40ms

QnPRHCPU User's

Manual (Redundant

System)

0.5 to 2000ms (configurable in increments of 0.5 ms) Set parameter values to specify

124k step

(496k byte)

252k step

(1008k byte)

124k step

(496k byte)

252k step

(1008k byte)

124k step

(496k byte)

252k step

(1008k byte)

Section 5.1,Section 5.2

496k byte 1008k byte 496k byte 1008k byte 496k byte 1008k byte

Section 5.1.1,

Section 5.2.1

Capacity of loading memory cards (2Mbyte max.)

Section 5.2.4

Installed memory card capacity(Flash card: 4 Mbyte max., ATA card: 32 Mbyte max.)

Section 5.2.4

256k byte

*3

Section 5.1.3,

Section 5.2.3

496k byte 1008k byte 496k byte 1008k byte 496k byte 1008k byte

Section 5.1.2,

Section 5.2.2

8k byte ----

QCPU User's Manual

(Multiple CPU System)

Loading...

Loading...