11. DMAC

puorG92/C61M

page 98

854fo7002,03.raM21.1.veR

2110-1010B90JER

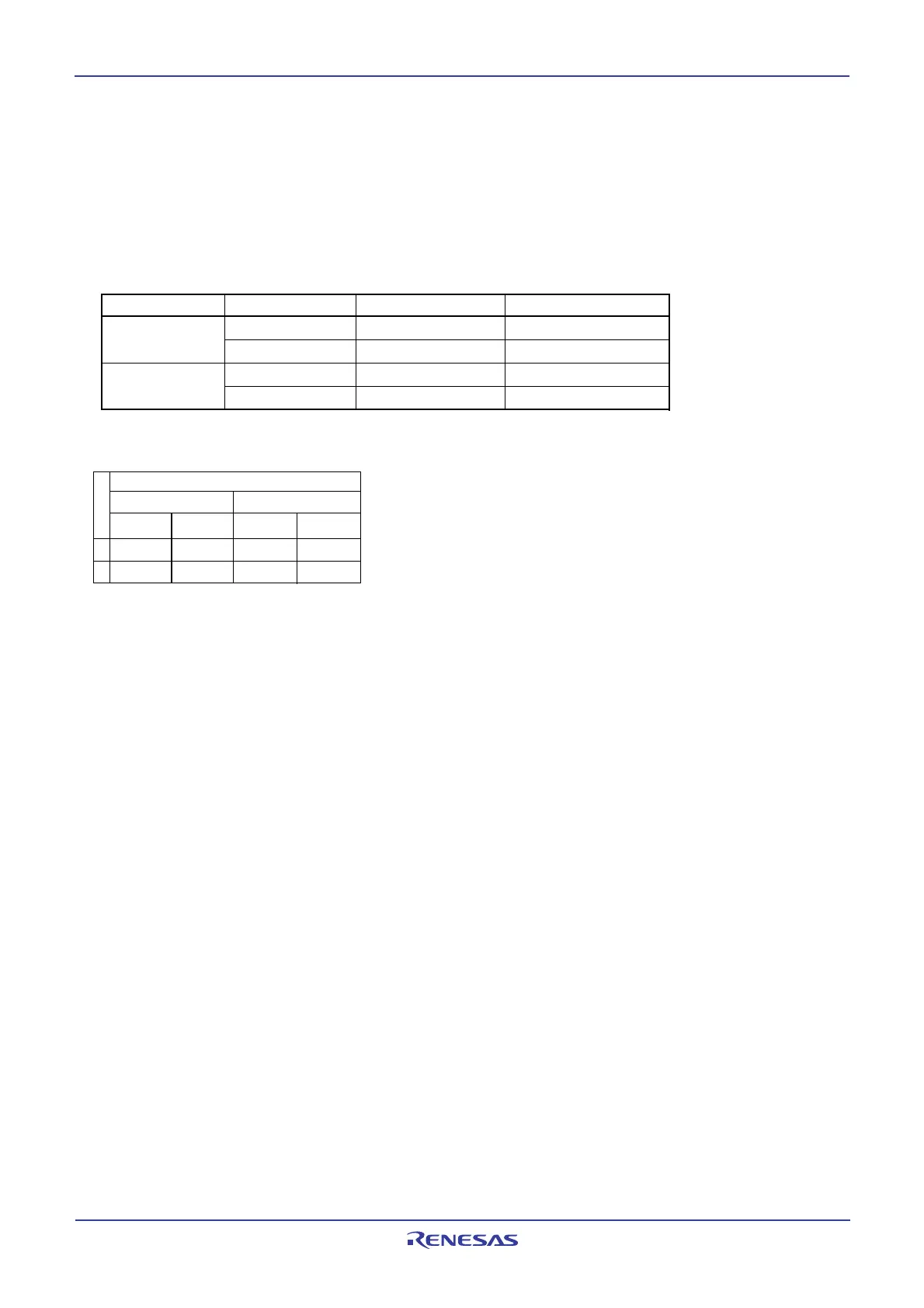

Table 11.2 DMA Transfer Cycles

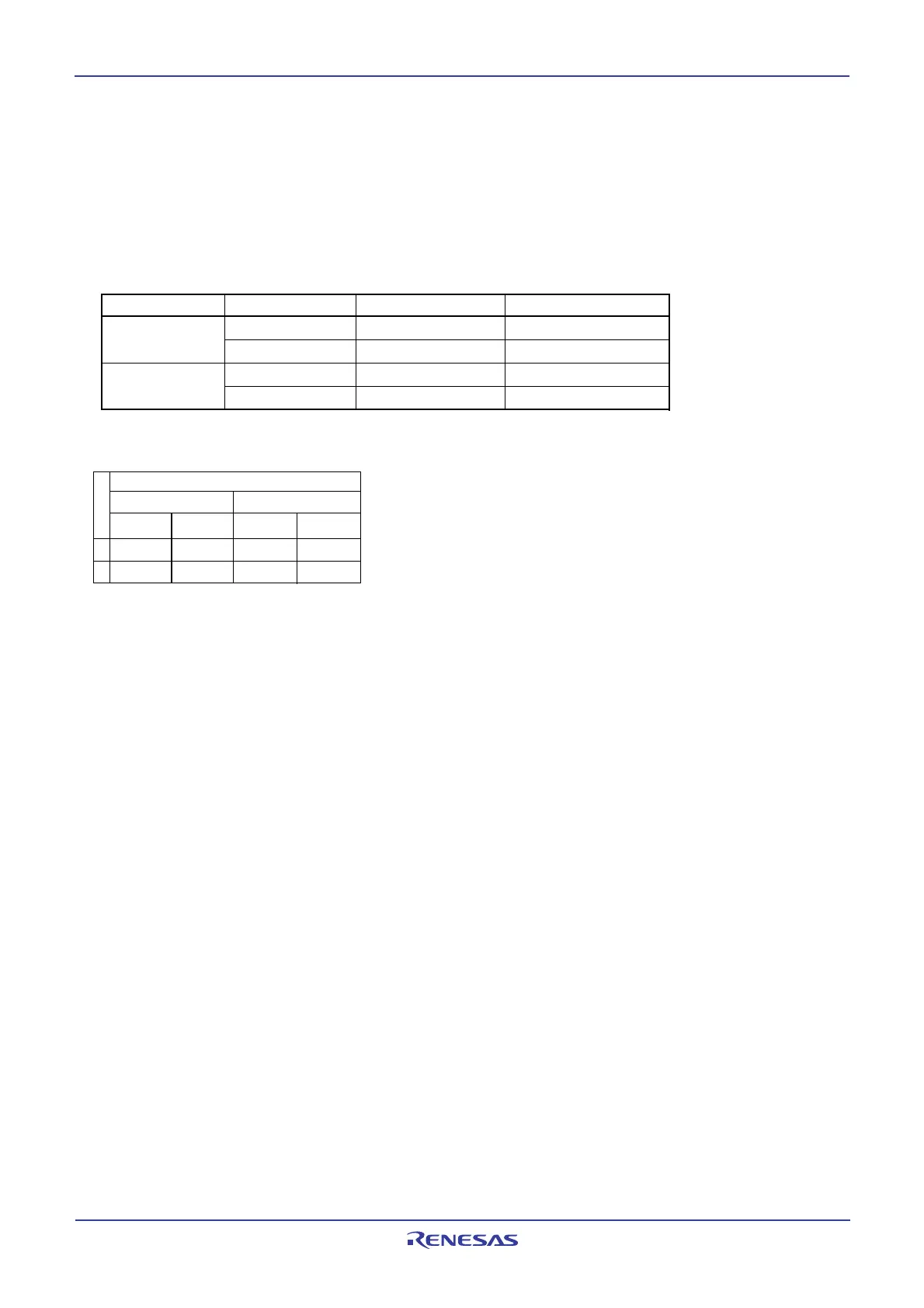

Table 11.3 Coefficient j, k

11.2. DMA Transfer Cycles

Any combination of even or odd transfer read and write adresses is possible. Table 11.2 shows the

number of DMA transfer cycles. Table 11.3 shows the Coefficient j, k.

The number of DMAC transfer cycles can be calculated as follows:

No. of transfer cycles per transfer unit = No. of read cycles x j + No. of write cycles x k

Transfer unit Access address No. of read cycles No. of write cycles

8-bit transfers Even 1 1

(DMBIT= 1) Odd 1 1

16-bit transfers Even 1 1

(DMBIT= 0) Odd 2 2

Internal Area

Internal ROM, RAM SFR

No wait With wait

1

1

2

2

2

2

j

k

3

3

1 wait

2 wait

(1)

(1)

NOTE:

1. Depends on the set value of PM20 bit in PM2 register

Loading...

Loading...