20. Flash Memory Version

puorG92/C61M

page 351

854fo7002,03.raM21.1.veR

2110-1010B90JER

20.8 Status Register

The status register indicates the operating status of the flash memory and whether or not erase or pro-

gram operation is successfully completed. Bits FMR00, FMR06, and FMR07 in the FMR0 register indi-

cate the status of the status register.

Table 20.6 lists the status register.

In EW mode 0, the status register can be read in the following cases:

(1) Any even address in the user ROM area is read after writing the read status register command

(2) Any even address in the user ROM area is read from when the program or block erase command is

executed until when the read array command is executed.

20.8.1 Sequence Status (SR7 and FMR00 Bits )

The sequence status indicates the flash memory operating status. It is set to 0 (busy) while the auto-

program and auto-erase operation is being executed and 1 (ready) as soon as these operations are

completed. This bit indicates 0 (busy) in erase-suspend mode.

20.8.2 Erase Status (SR5 and FMR07 Bits)

Refer to 20.8.4 Full Status Check.

20.8.3 Program Status (SR4 and FMR06 Bits)

Refer to 20.8.4 Full Status Check.

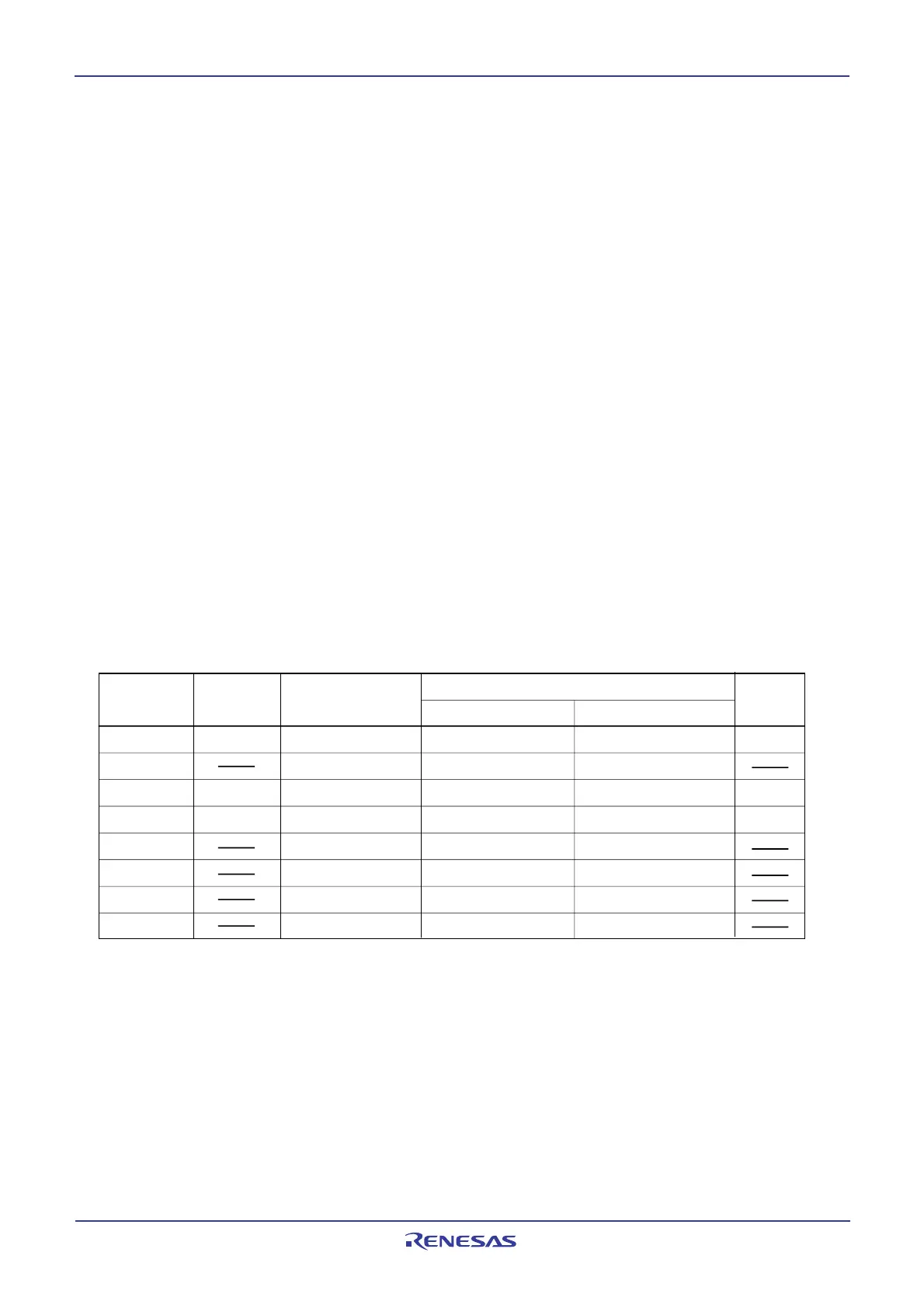

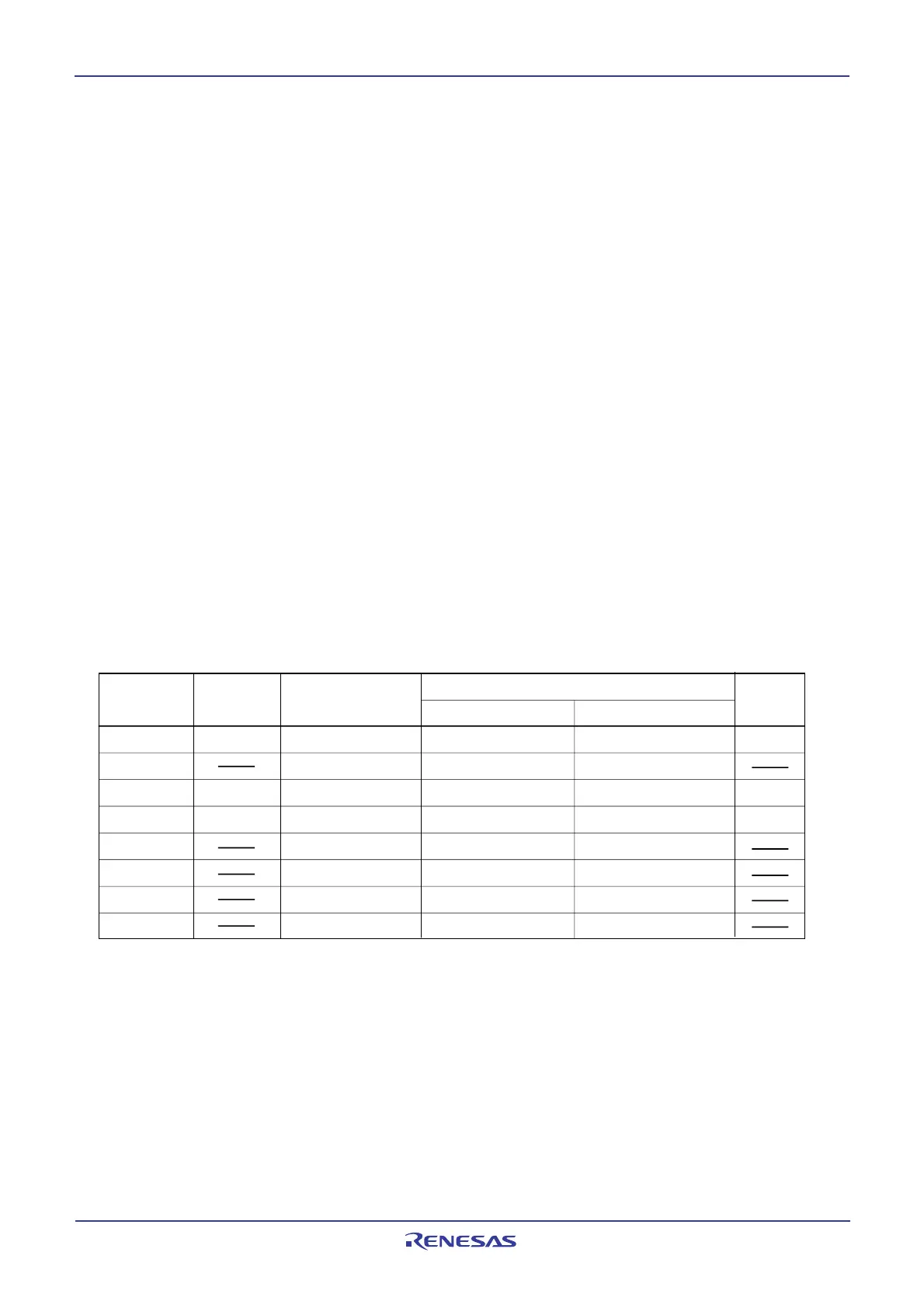

Table 20.6 Status Register

• D7 to D0: Indicates the data bus which is read out when executing the read status register command.

• The FMR07 bit (SR5) and FMR06 bit (SR4) are set to 0 by executing the clear status register command.

•

When the FMR07 bit (SR5) or FMR06 bit (SR4) is set to 1, the program and block erase command are not accepted.

Bits in the

SRD Register

SR4 (D

4)

SR5 (D

5)

SR7 (D

7)

SR6 (D

6)

Status

Name

Contents

SR1 (D

1)

SR2 (D

2)

SR3 (D

3)

SR0 (D

0)

Program status

Erase status

Sequence status

Reserved

Reserved

Reserved

Reserved

1

Ready

Terminated by error

Terminated by error

-

-

-

-

-

0

Busy

Completed normally

Completed normally

-

-

-

-

-

Reserved

Bits in the

FMR0

Register

FMR00

FMR07

FMR06

Value

After

Reset

1

0

0

Loading...

Loading...