16. MULTI-MASTER I

2

C bus INTERFACE

puorG92/C61M

page 275

854fo7002,03.raM21.1.veR

2110-1010B90JER

16.7 I

2

C0 Control Register 2 (S4D0 Register)

The S4D0 register controls the error communication detection.

If the SCL clock is stopped counting dring data transfer, each device is stopped, staying online. To avoid

the situation, the I

2

C bus interface circuit has a function to detect the time-out when the SCL clock is

stopped in high-level ("H") state for a specific period, and to generate an I

2

C bus interface interrupt request.

See Figure 16.13.

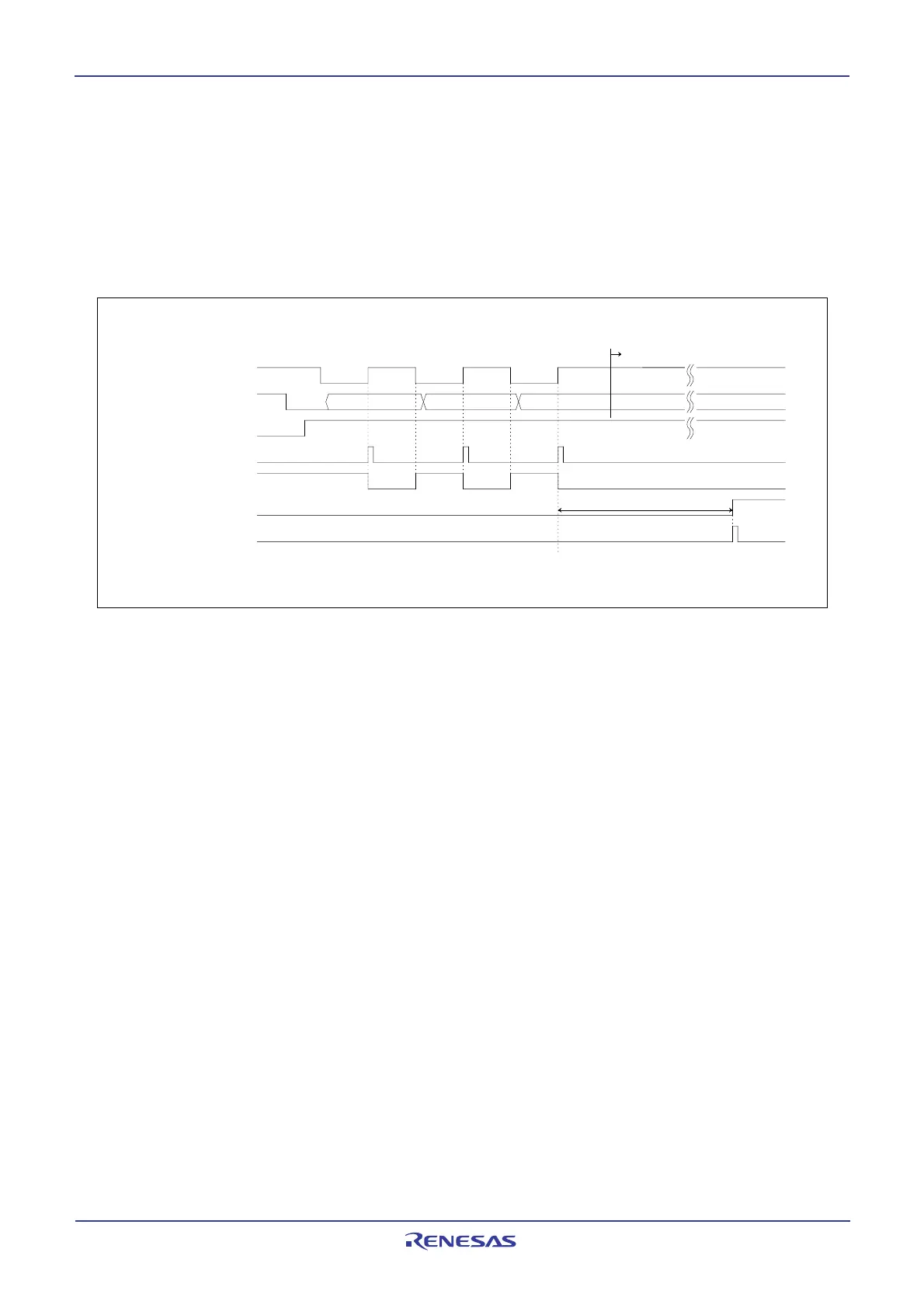

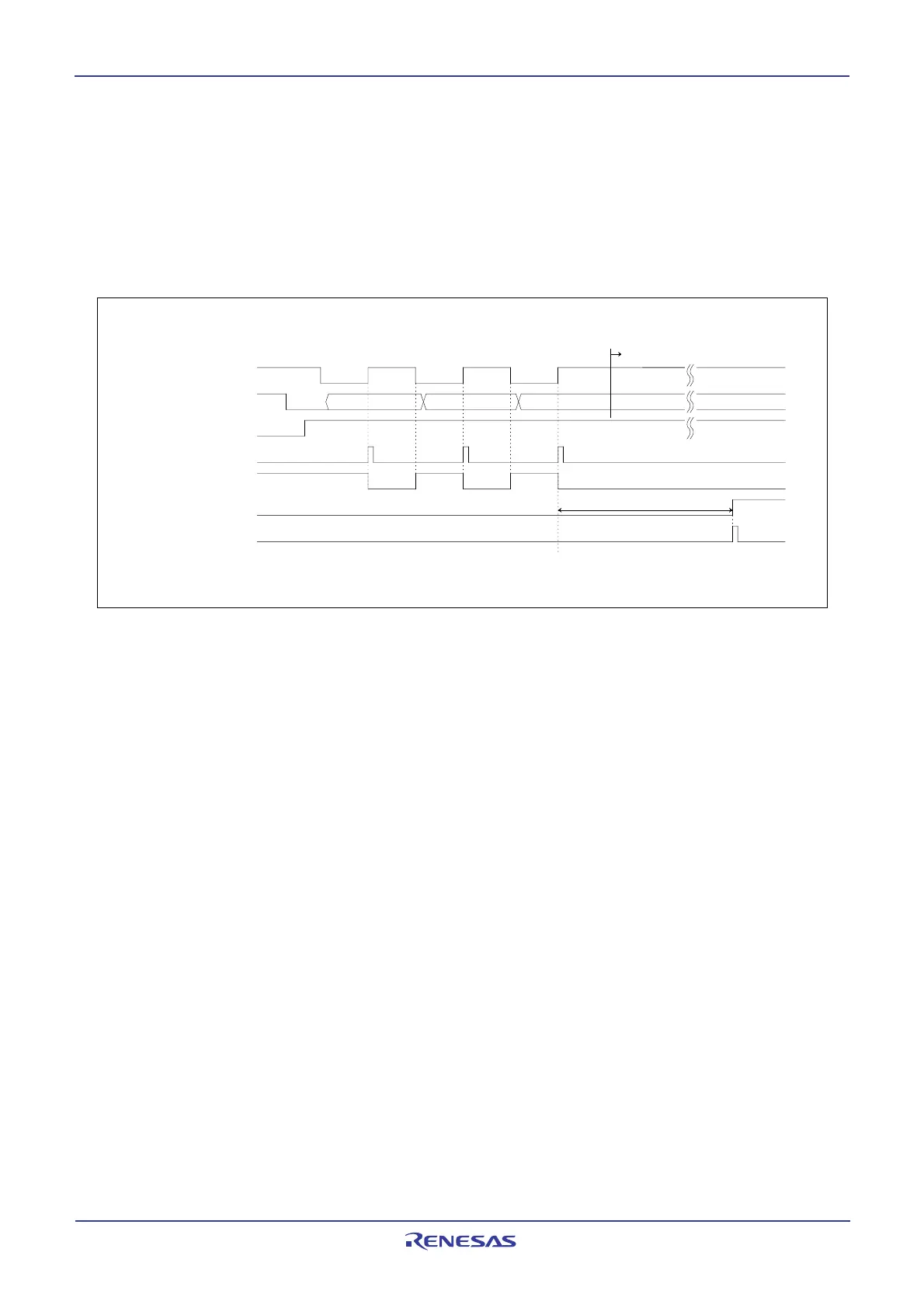

Figure 16.13 The timing of time-out detection

1 clock

1 bit

S

CL

S

DA

BB flag

Internal counter start signal

Internal counter stop, reset signal

Internal counter overflow signal

I

2

C-bus interface interrupt

request signal

2 bit 3 bit

2 clock 3 clock

S

CL

clock stop (“H”)

The time of timeout detection

Loading...

Loading...