15. A/D Converter

puorG92/C61M

page 222

854fo7002,03.raM21.1.veR

2110-1010B90JER

15. A/D Converter

Note

Ports P04 to P07(AN04 to AN07), P10 to P13(AN20 to AN23) and P95 to P97(AN25 to AN27) are not

available in 64-pin package. Do not use port P04 to P07(AN04 to AN07), P10 to P13(AN20 to AN23)

and P95 to P97(AN25 to AN27) as analog input pins in 64-pin package.

The MCU contains one A/D converter circuit based on 10-bit successive approximation method configured

with a capacitive-coupling amplifier. The analog inputs share the pins with P100 to P107 (AN0 to AN7), P00

to P07 (AN00 to AN07), and P10 to P13, P93, P95 to P97 (AN20 to AN27), and P90 to P92 (AN30 to AN32).

____________

Similarly, ADTRG input shares the pin with P15. Therefore, when using these inputs, make sure the corre-

sponding port direction bits are set to 0 (input mode).

When not using the A/D converter, set the VCUT bit to 0 (Vref unconnected), so that no current will flow

from the Vref pin into the resistor ladder, helping to reduce the power consumption of the chip.

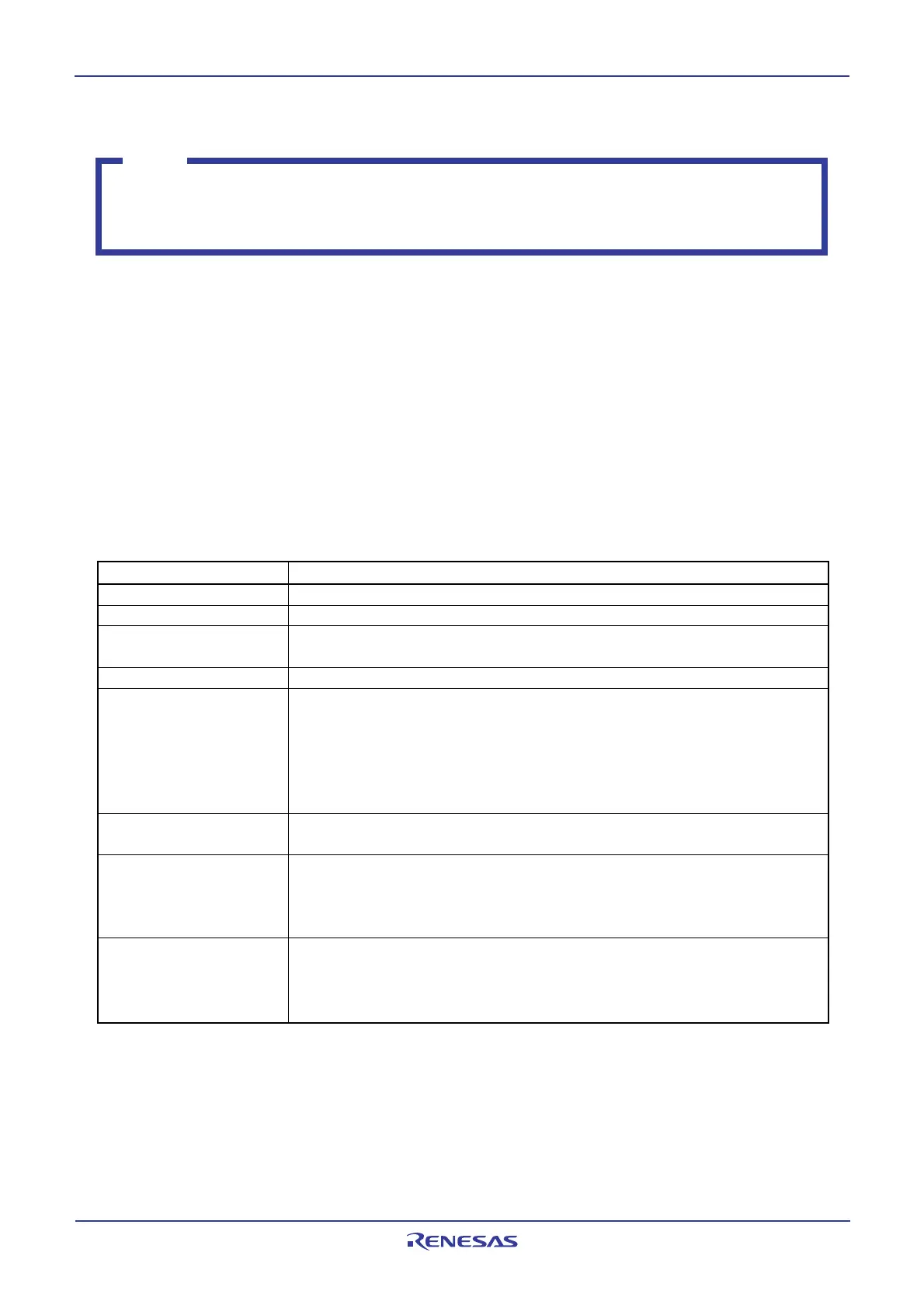

The A/D conversion result is stored in the ADi register bits for ANi, AN0i, AN2i (i = 0 to 7), and AN3i pins (i

= 0 to 2). Table 15.1 shows the A/D converter performance. Figure 15.1 shows the A/D converter block

diagram and Figures 15.2 to 15.4 show the A/D converter associated with registers.

Item Performance

A/D Conversion Method Successive approximation (capacitive coupling amplifier)

Analog Input Voltage

(1)

0V to AVCC (VCC)

Operating Clock φAD

(2)

fAD/divided-by-2 or fAD/divided-by-3 or fAD/divided-by-4 or fAD/divided-by-6

or fAD/divided-by-12 or fAD

Resolution 8-bit or 10-bit (selectable)

Integral Nonlinearity Error When AVCC = Vref = 5V

• With 8-bit resolution: ±2LSB

• With 10-bit resolution: ±3LSB

When AVCC = Vref = 3.3V

• With 8-bit resolution: ±2LSB

• With 10-bit resolution: ±5LSB

Operating Modes

One-shot mode, repeat mode, single sweep mode, repeat sweep mode 0, repeat

sweep mode 1, simultaneous sample sweep mode and delayed trigger mode 0,1

Analog Input Pins

8 pins (AN0 to AN7) + 8 pins (AN00 to AN07) + 8 pins (AN20 to AN27) + 3 pins (AN30

to AN32) (80-pin package)

8 pins (AN0 to AN7) + 4 pins (AN00 to AN03) + 1 pin (AN24) + 3 pins (AN30 to AN32)

(64-pin package)

Conversion Speed Per Pin

• Without sample and hold function

8-bit resolution: 49

φAD

cycles

,

10-bit resolution: 59

φAD

cycles

• With sample and hold function

8-bit resolution: 28

φAD

cycles

,

10-bit resolution: 33

φAD

cycles

Table 15.1 A/D Converter Performance

NOTES:

1. Not dependent on use of sample and hold function.

2. Set the φAD frequency to 10 MHz or less.

Without sample-and-hold function, set the φAD frequency to 250kH

Z or more.

With the sample and hold function, set the φAD frequency to 1MH

Z or more.

Loading...

Loading...