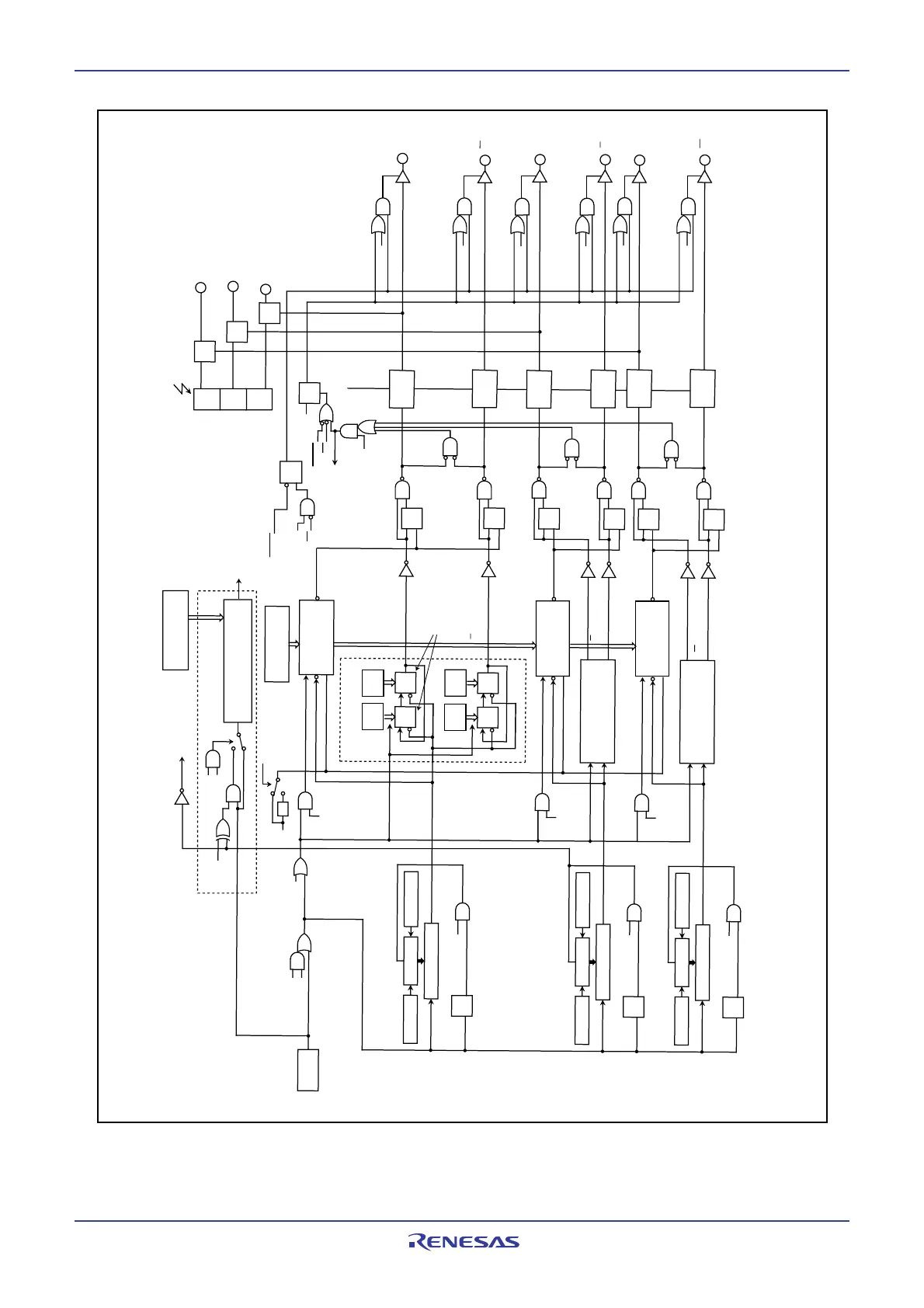

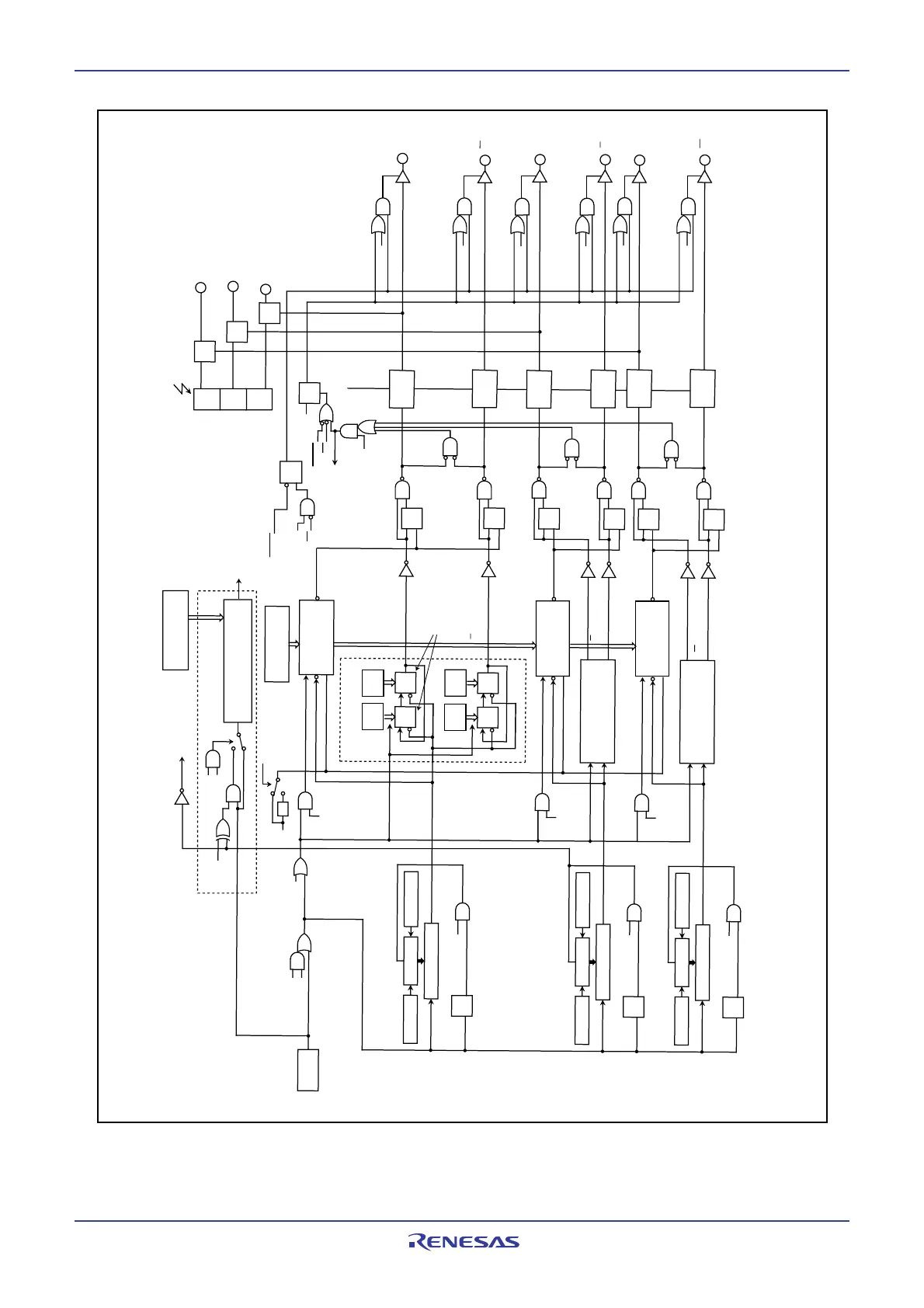

12. Timer (Three-phase Motor Control Timer Function)

D

R

Q

0

INV12

1

Trigger

Trigger

Timer B2

(Timer mode)

Signal to be

written to

timer B2

1

Timer B2

interr

upt requ

est bit

DU1

bit

D

T

Q

Q

Q

U

Three-phase output

shift register

(U phase)

Dead tim

e timer

n = 1

to 255

Trigger

Trigger

Reload register

Trigger

Trigger

U

phase output signal

U

phase output signal

V

W

phase output signal

W

phase output signal

W

phase output

control circuit

D

Q

T

D

Q

T

W

D

Q

T

D

Q

T

V

D

Q

T

D

Q

T

U

W

V

U

Reload

Timer A1 cou

nt

er

(One-shot timer mode)

Trigger

T

Q

Reload

Timer A2 count

er

(One-shot timer mode)

Trigger

T

Q

Reload

Timer A4 count

er

(One-shot timer mode)

Trigger

T

Q

Transfer trigger

(Note 1)

Timer B2 underflow

DU0

bit

DUB0

bit

TA4 register

TA41

register

TA1

register

TA11

register

TA2

register

TA21

register

Timer Ai (i = 1, 2, 4) start trigger signal

Timer A4 reload control signal

Timer A4

one-shot pulse

DUB1

bit

Dead time timer

n = 1 to 2

55

Dead time timer

n = 1 to 255

Interrupt occurrence set circuit

ICTB2 register

n = 1 to 15

0

INV13

ICTB2 counter

n = 1 to 15

SD

RESET

INV03

INV14

INV05

INV04

INV00

INV01

INV11

INV11

INV11

INV11

INV06

INV06

INV06

INV07

INV10

1/2

f1

or f

2

phase output

control circuit

phase outpu

t

control circuit

V p

hase output signal

V phase output

signal

Reverse

control

Rev

erse

control

Reverse

control

Reverse

control

Reverse

control

D

T

D

T

Q

D

T

Reverse

control

IDW

IDV

IDU

D

Q

T

D

Q

T

D

Q

T

b2

b0

b1

Bits 2 through 0 of Position-data-

retain function control register

(address 034E

16

)

PD8_0

PD8_1

PD7_2

PD7_3

PD7_4

PD7_5

S

Q

R

RESET

SD

IVPRC1

Data Bus

n = 1 to 255

NOTE:

1. If the INV06 bit is set to 0 (triangular wave modulation mode), a transfer trigger is generated at only the first occurrence of a timer B2 underflow after writing to the IDB0 and IDB1 registers.

Set to 0 when TA2S bit is set to 0

Set to 0 when TA1S bit = 0

Set to 0 when TA4S bit is set to 0

Diagram for switching to P8

0

, P81 and P7

2

- P7

5

is not shown.

Loading...

Loading...