13. Timer S

puorG92/C61M

page 145

854fo7002,03.raM21.1.veR

2110-1010B90JER

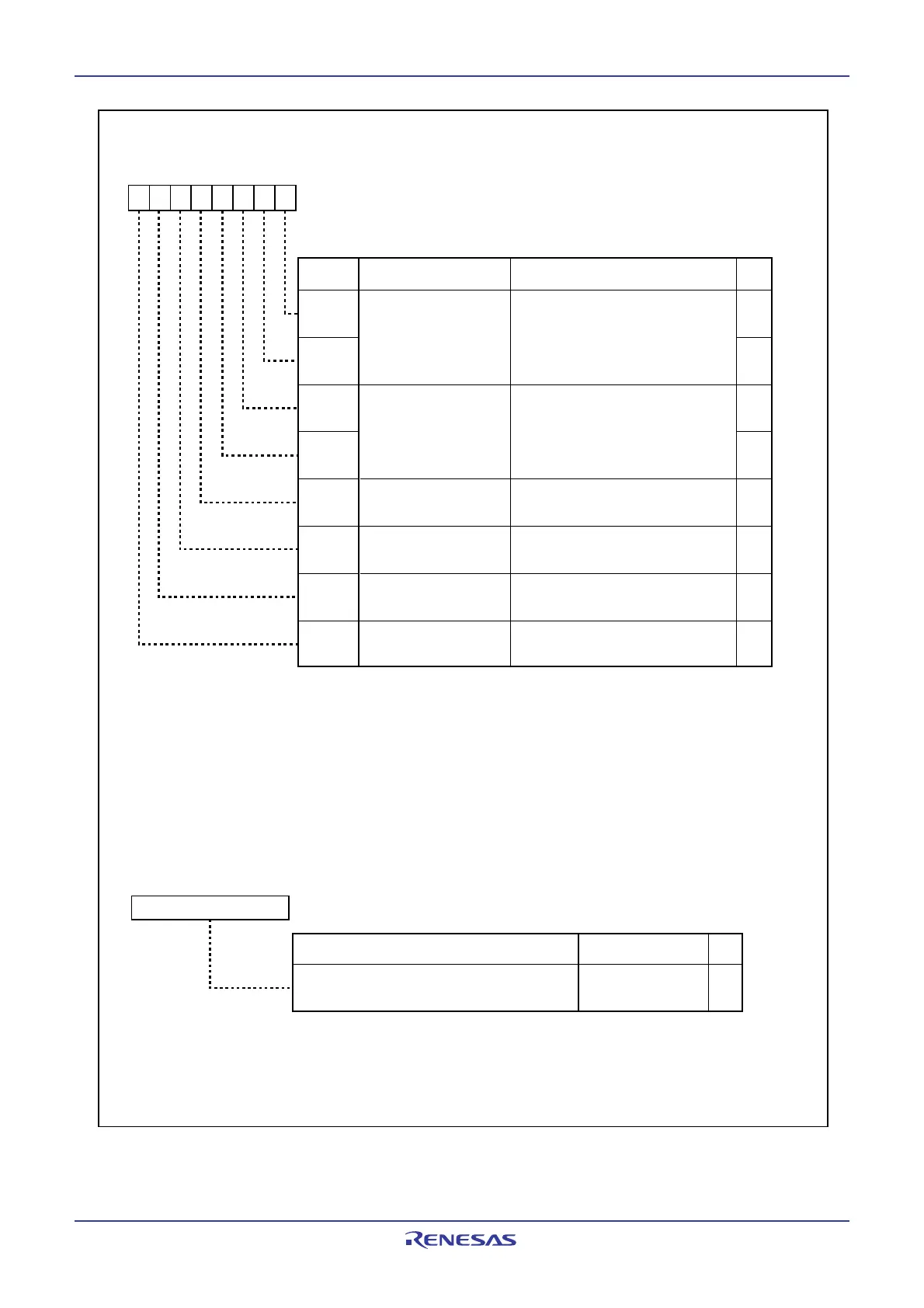

Figure 13.5 G1TMCR0 to G1TMCR7 Registers, and G1TPR6 to G1TPR7 Registers

Time Measurement Control Register j (j=0 to 7)

Symbol

G1TMCR0 to G1TMCR3

G1TMCR4 to G1TMCR7

Address

0318

16

, 0319

16

, 031A

16

, 031B

16

031C

16

, 031D

16

, 031E

16

, 031F

16

After Reset

00

16

00

16

RW

RW

RW

RW

RW

RW

RW

RW

RW

Bit Name Function

Bit

Symbol

CTS0

CTS1

DF0

Time measurement

trigger select bit

DF1

Gate function

select bit

(2)

GT

GOC

PR

GSC

Digital filter function

select bit

Gate function clear

select bit

(2, 3, 4)

0: Gate function is not used

1: Gate function is used

Gate function clear

bit

(2, 3)

Prescaler function

select bit

(2)

b1

0

0

1

1

b0

0

1

0

1

: No time measurement

: Rising edge

: Falling edge

: Both edges

b3

0

0

1

1

b2

0

1

0

1

: No digital filter

: Do not set to this value

: f

BT1

: f

1

or f

2

(1)

0: Not cleared

1: The gate is cleared when the base

timer matches the G1POk register

The gate is cleared by setting the

GSC bit to 1

0: Not used

1: Used

NOTES:

1. When the PCLK0 bit in the PCLKR register is set to 0, the count source is f

2 cycles. And when the

PCLK0 bit is set to 1, the count source is f

1 cycles.

2. These bits are in registers G1TMCR6 and G1TMCR7. Set all bits 4 to 7 in registers G1TMCR0 to

G1TMCR5 to 0.

3. These bits are enabled when the GT bit is set to 1.

4. The GOC bit is set to 0 after the gate function is cleared. See Figure 13.7 for details on the G1POk

register (k=4 when j=6 and k=5 when j=7).

b7 b6 b5 b4 b3 b2 b1 b0

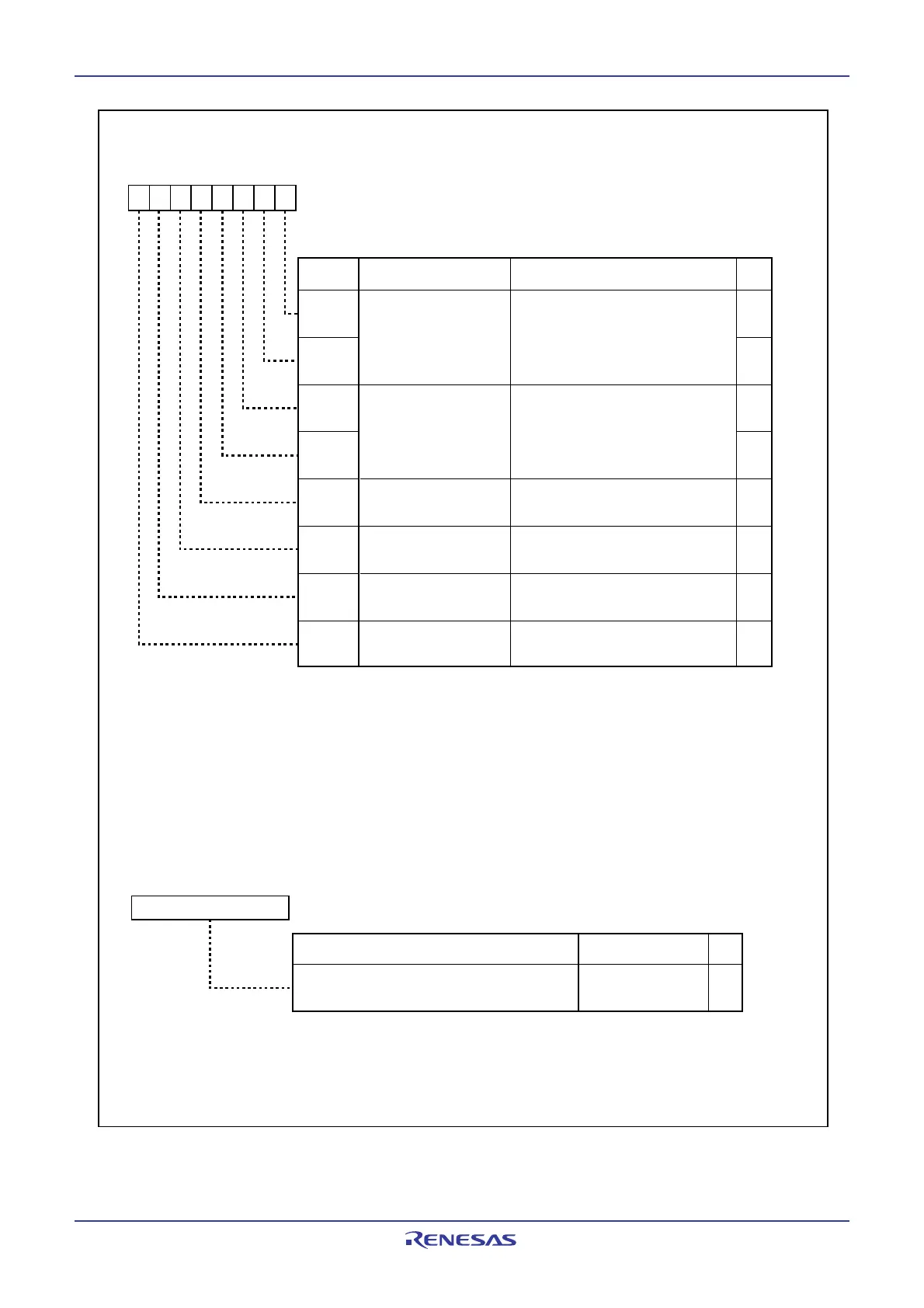

Time Measurement Prescale Register j (j=6,7)

(1)

Symbol Address After Reset

G1TPR6 to G1TPR7 0324

16

, 0325

16

00

16

RW

RW

Function Setting Range

As the setting value is n, time is measured when-

ever a trigger input is counted by n+1

(2)

0016 to FF16

NOTES:

1. The G1TPR6 to G1TPR7 registers reflect the base timer value, synchronizing with the count source

f

BT1 cycles.

2. The first prescaler, after the PR bit in the G1TMCRj register is changed from 0 (not used) to 1

(used), may be divided by n, rather than n+1. The subsequent prescaler is divided by n+1.

b7 b0

Loading...

Loading...