13. Timer S

puorG92/C61M

page 144

854fo7002,03.raM21.1.veR

2110-1010B90JER

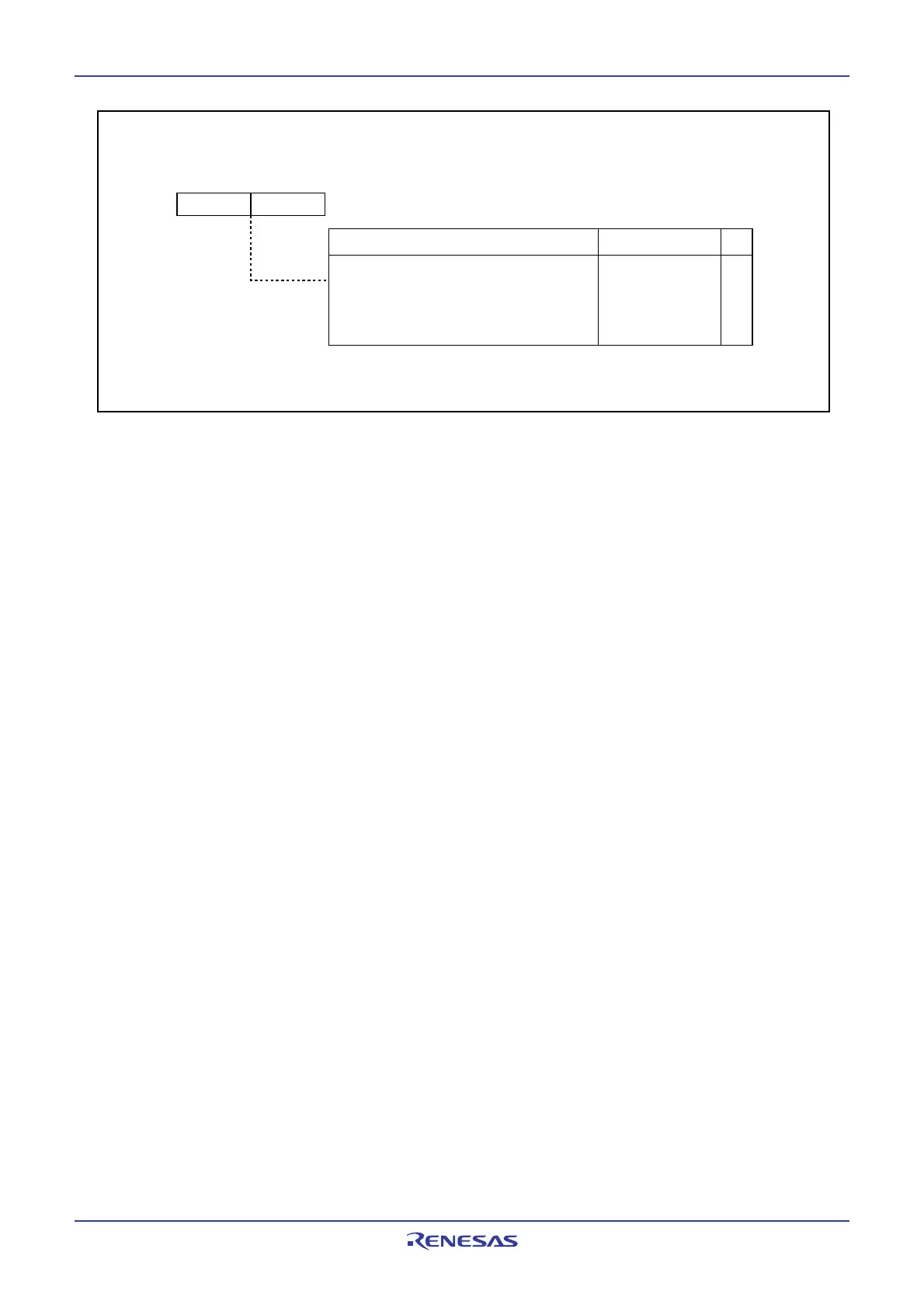

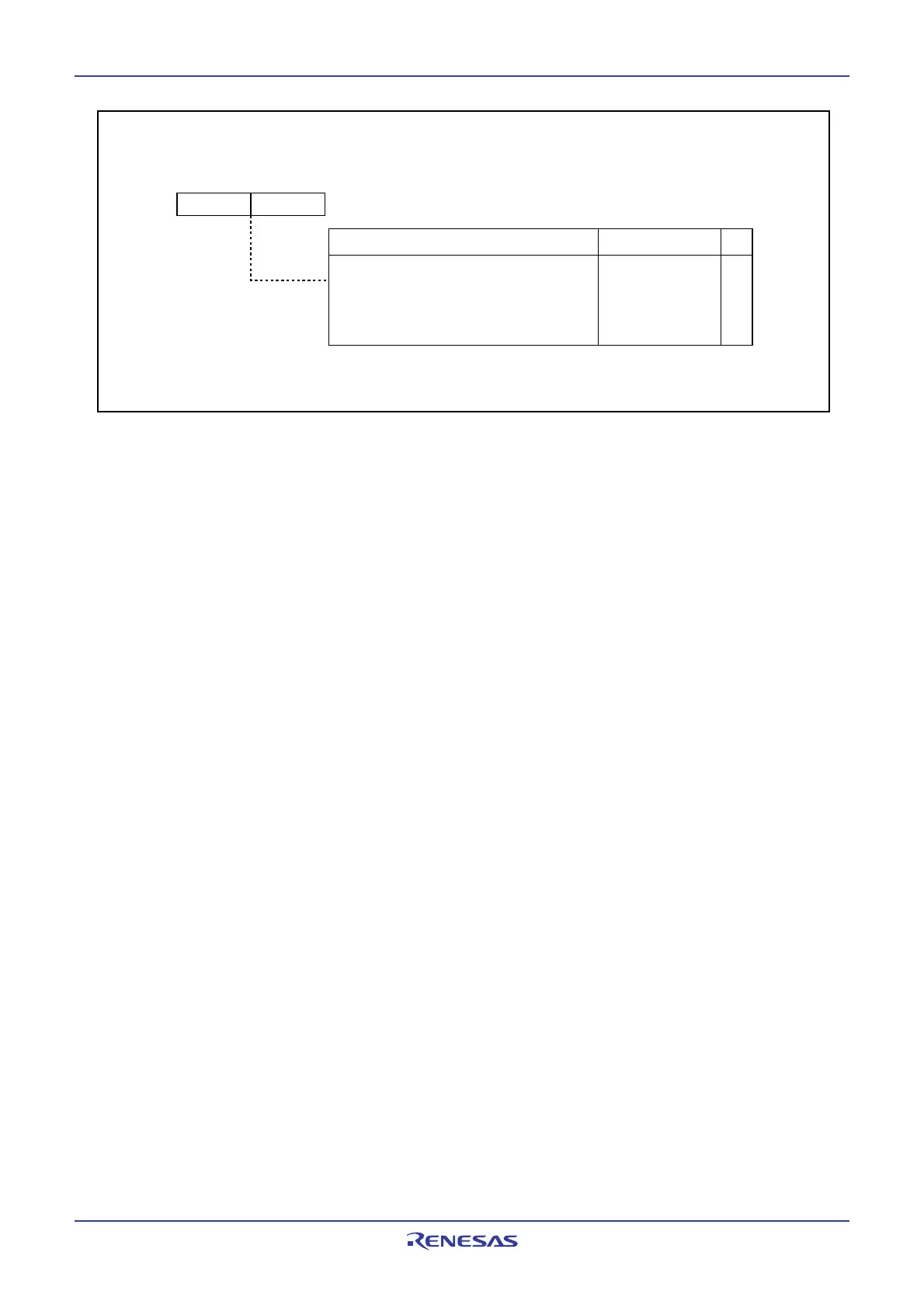

Figure 13.4 G1BTRR Register

Base Timer Reset Register

(1)

Symbol Address After Reset

G1BTRR 0329

16 - 032816 Undefined

RW

RW

Function Setting Range

When enabled by the RST4 bit in the G1BCR0

register, the base timer is reset by matching the

G1BTRR register setting value and the base

timer setting value.

0000

16 to FFFF16

b15

b0b7

b8

(b7) (b0)

NOTE:

1.

The G1BTRR register reflects the value of the base timer, synchronizing with the count source fBT1 cycles.

Loading...

Loading...