13. Timer S

puorG92/C61M

page 165

854fo7002,03.raM21.1.veR

2110-1010B90JER

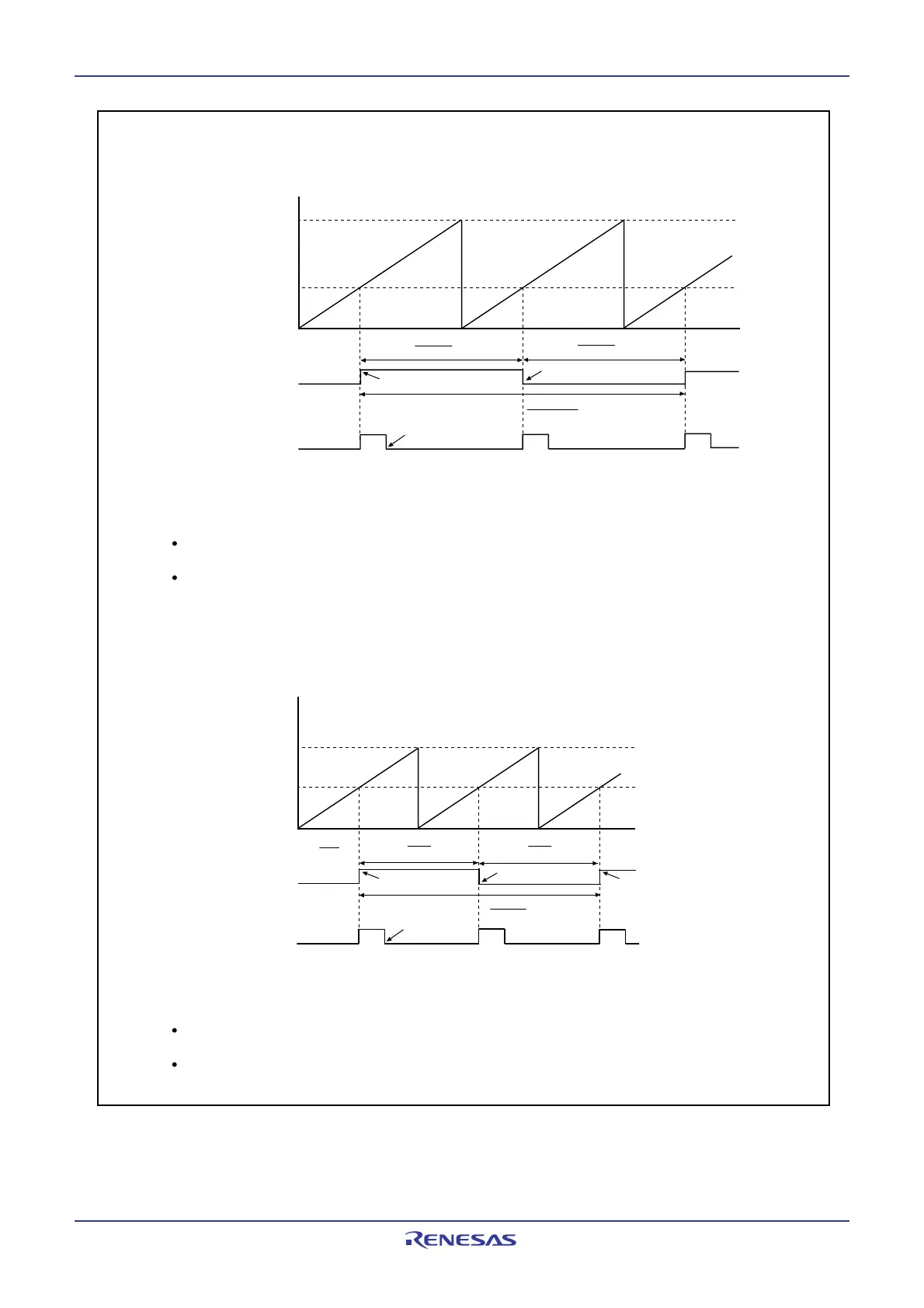

Figure 13.23 Phase-delayed Waveform Output Mode

FFFF

16

m

65536

f

BT1

65536X2

f

BT1

0000

16

FFFF

16

m

n+2

0000

16

65536

f

BT1

m

f

BT1

n+2

f

BT1

n+2

f

BT1

2(n+2)

f

BT1

Base timer

(1) Free-running operation

(Bits RST4, RST2, and RST1 in the registers G1BCR0 and G1BCR1 are set to 0)

OUTC1j pin

G1IRj bit

j=0 to 7

m : Setting value of the G1POj register

G1IRj bit : Bits in the G1IR register

Inverse

Write 0 by program

if setting to 0

Inverse

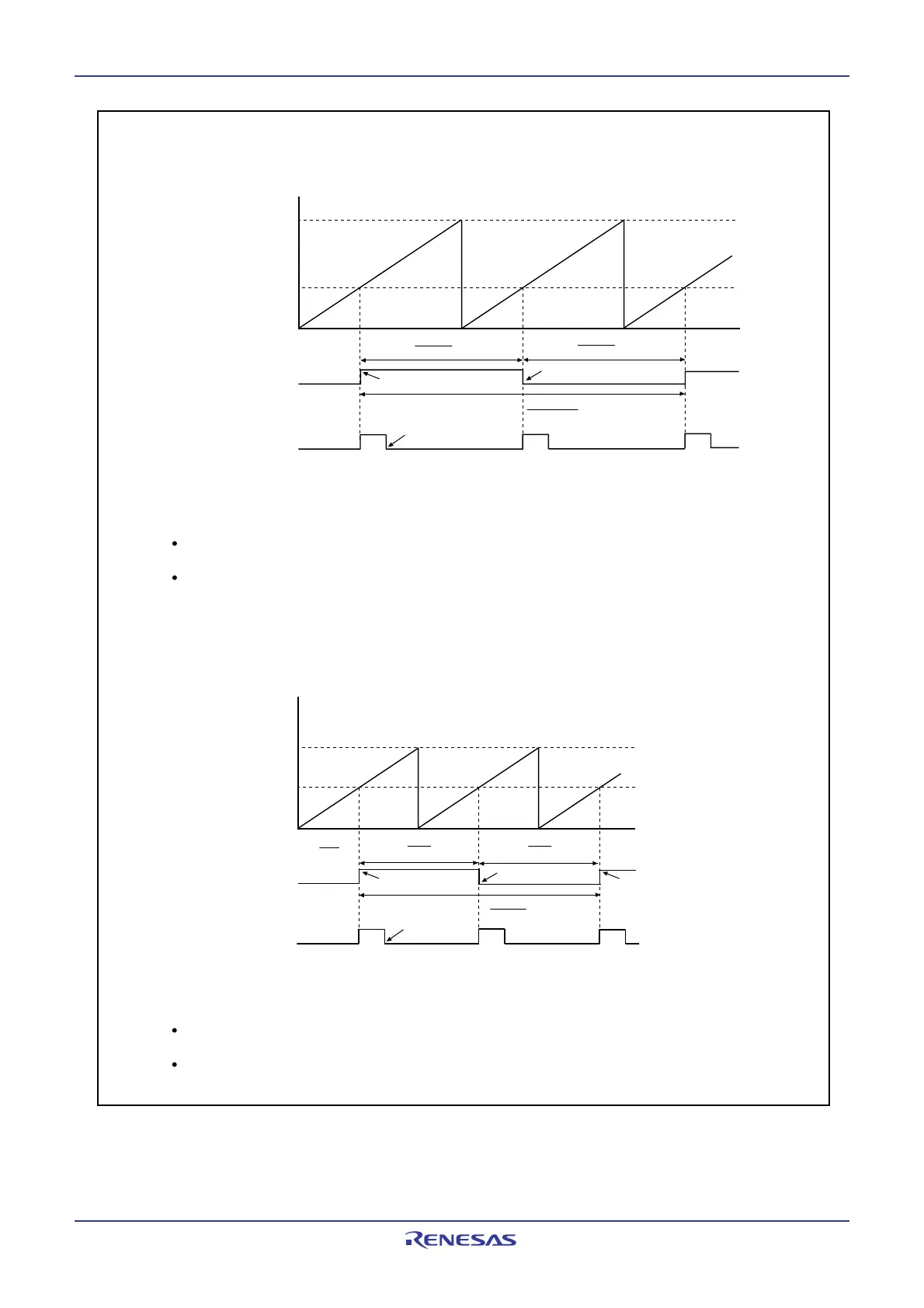

(2) Base timer is reset when the base timer matches either following register

(a) G1PO0 (enabled by setting bit RST1 to 1, and bits RST4 and RST2 to 0), or

(b) G1BTRR (enabled by setting bit RST4 to 1, and bits RST2 and RST1 to 0)

G1IRj bit

OUTC1j pin

Base timer

Write 0 by program

if setting to 0

Inverse

j=1 to 7

m : Setting value of the G1POj register n: Setting value of either register G1PO0 or G1BTRR

G1IRj bit : Bits in the G1IR register

The above applies under the following conditions.

The IVL bit in the G1POCRj register is set to 0 (L output as a default value).

The INV bit is set to 0 (not inversed).

Bits UD1 to UD0 are set to 00

2

(counter increment mode).

The above applies under the following conditions.

The IVL bit in the G1POCRj register is set to 0 (L output as a default value). The INV bit

is set to 0 (not inversed).

Bits UD1 to UD0 are set to 00

2

(counter increment mode).

Inverse

Inverse

Loading...

Loading...