14. Serial I/O

puorG92/C61M

page 215

854fo7002,03.raM21.1.veR

2110-1010B90JER

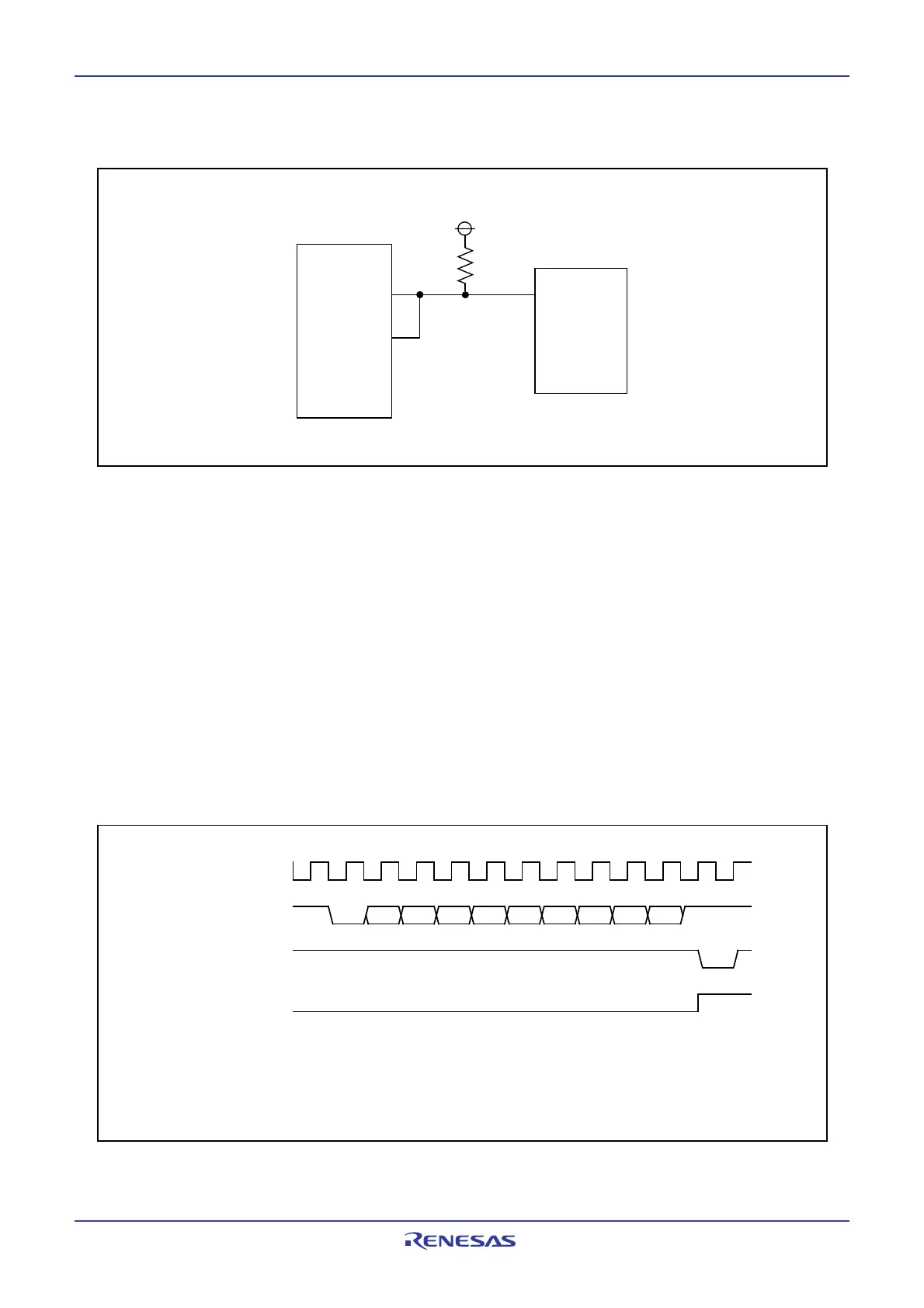

Figure 14.32 shows the example of connecting the SIM interface. Connect TXD2 and RXD2 and apply

pull-up.

Figure 14.32 SIM Interface Connection

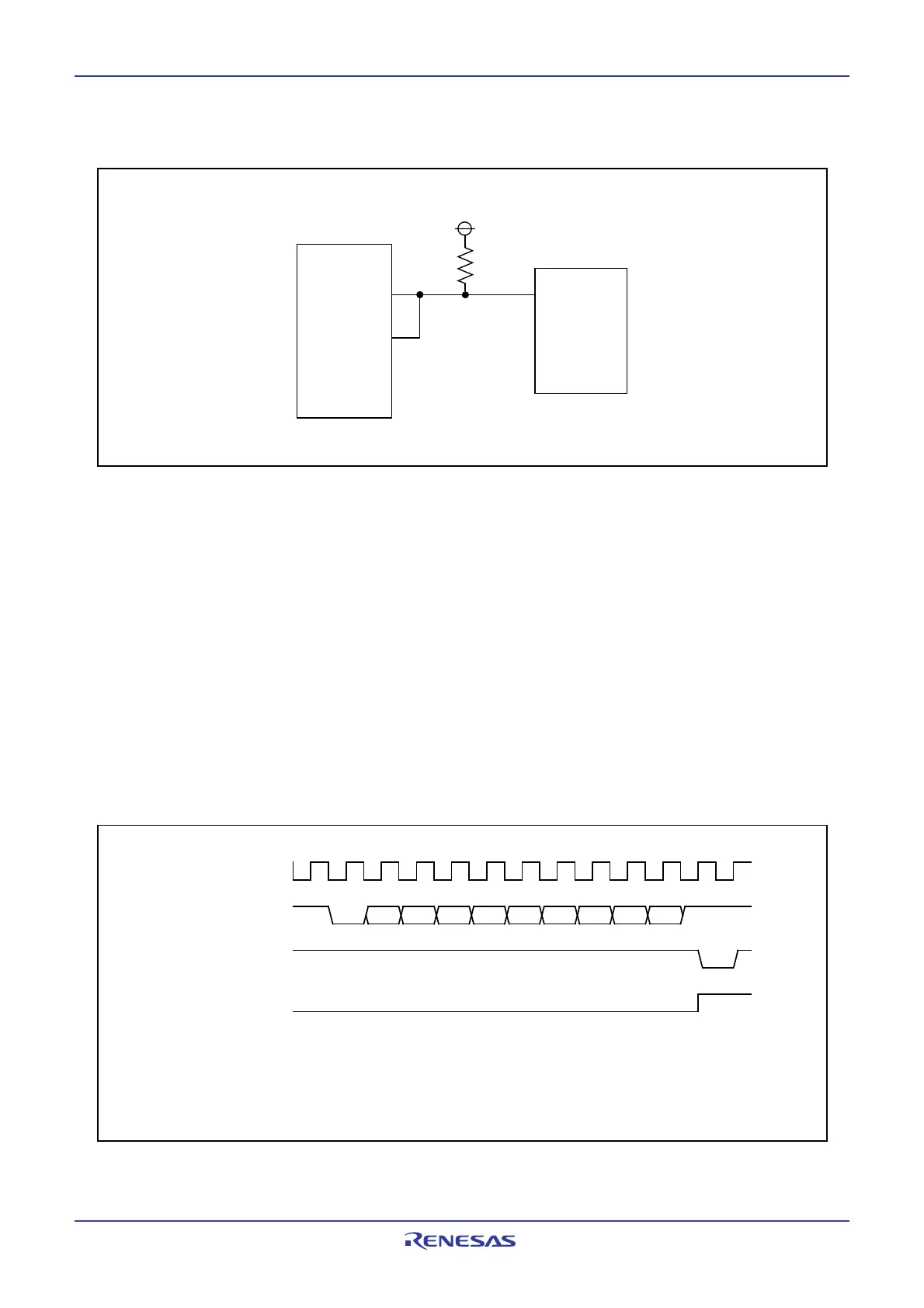

14.1.6.1 Parity Error Signal Output

The parity error signal is enabled by setting the U2ERE bit in theU2C1 register to 1.

• When receiving

The parity error signal is output when a parity error is detected while receiving data. This is achieved

by pulling the TxD2 output low with the timing shown in Figure 14.33. If the R2RB register is read

while outputting a parity error signal, the PER bit is cleared to 0 and at the same time the TxD2 output

is returned high.

• When transmitting

A transmission-finished interrupt request is generated at the falling edge of the transfer clock pulse

that immediately follows the stop bit. Therefore, whether a parity signal has been returned can be

determined by reading the port that shares the RxD2 pin in a transmission-finished interrupt service

routine.

Figure 14.33 Parity Error Signal Output Timing

MCU

SIM card

TxD

2

RxD2

D0 D1 D2 D3 D4 D5 D6 D7 PSPST

(1)

Transfer

clock

RxD

2

TxD2

U2C1 register

RI bit

“H”

“L”

“H”

“L”

“H”

“L”

1

0

This timing diagram applies to the case where the direct format is implemented.

NOTE:

1. The output of MCU is in the high-impedance state (pulled up externally).

ST: Start bit

P: Even Parity

SP: Stop bit

Loading...

Loading...