15. A/D Converter

puorG92/C61M

page 244

854fo7002,03.raM21.1.veR

2110-1010B90JER

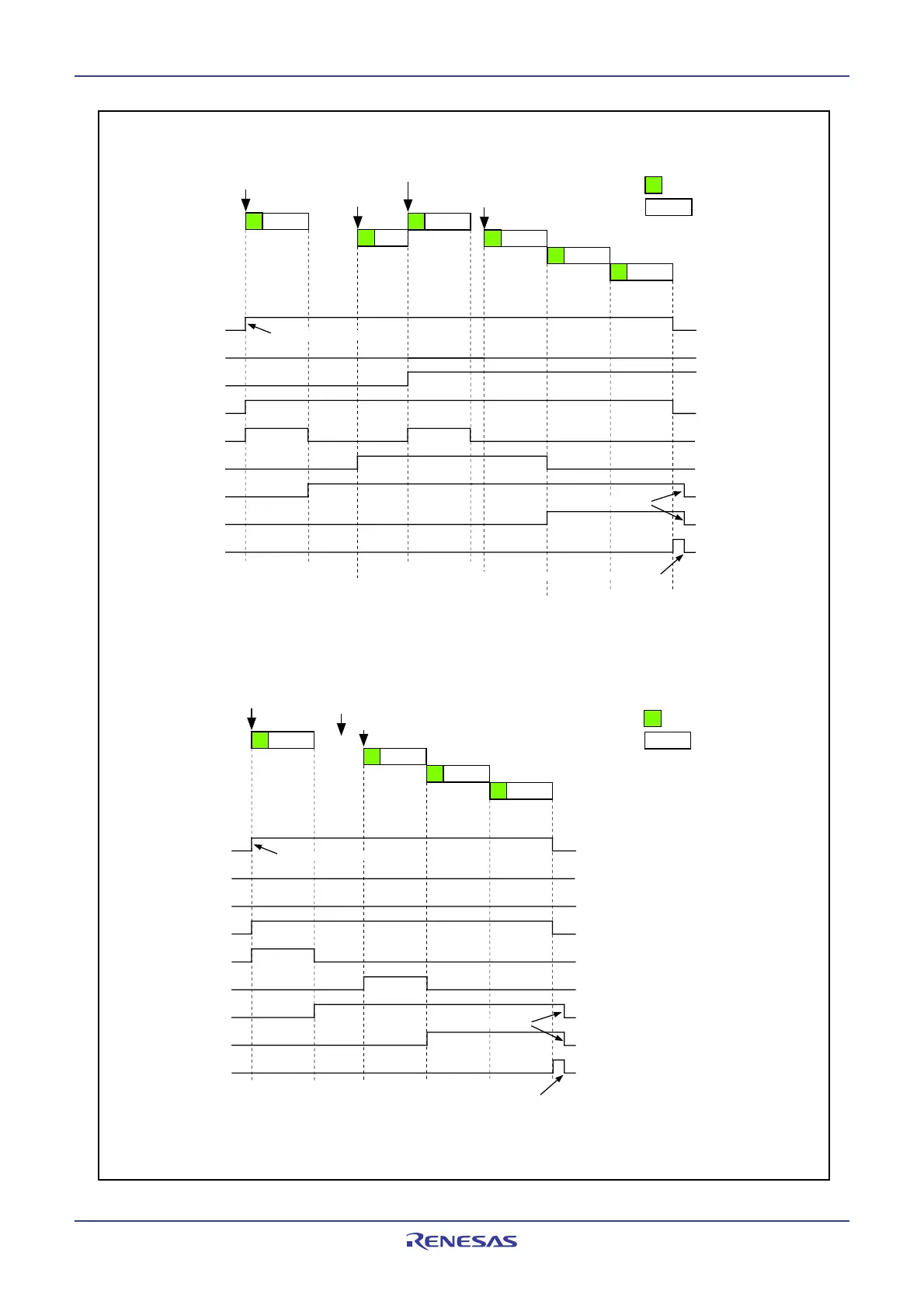

Figure 15.21 Each Flag Operation in ADSTAT0 Register Associated with the Operation

Example in Delayed Trigger Mode 0 (2)

AN0

AN1

AN2

AN3

Timer B0 underflow

(Abort othrt pins conversion )

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

AN0

AN1

AN2

AN3

Timrt B0 underflow

(An interrupt does not affect A/D conversion)

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

A/D pin input

voltage sampling

A/D pin conversion

A/D pin input

voltage sampling

A/D pin conversion

Do not set to 1 by program

Do not set to 1 by program

Set to 0 by interrupt request acknowledgement or a program

Set to 0 by interrupt request acknowledgement or a program

Set to 0 by program

Set to 0 by program

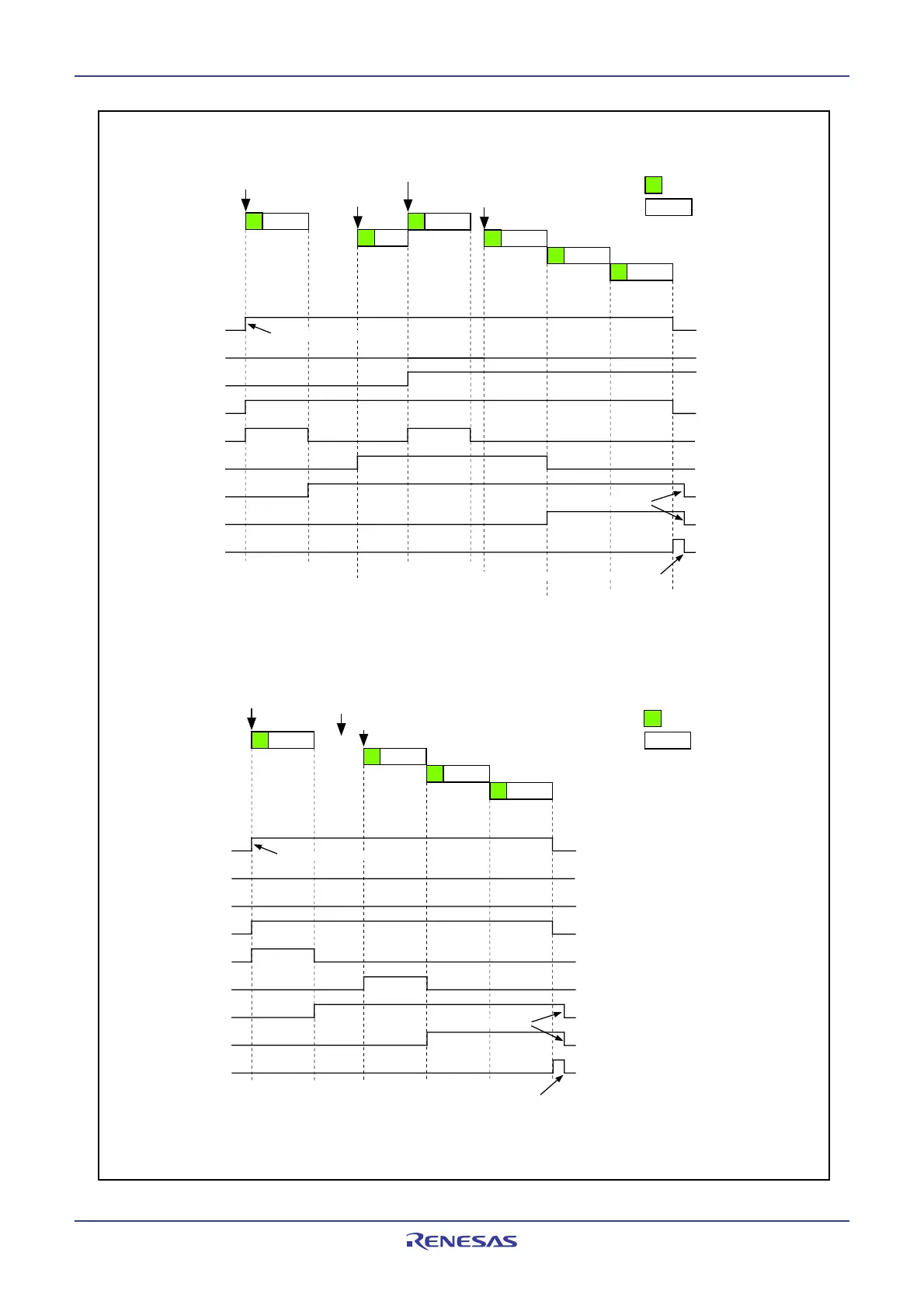

ADST flag: Bit 6 in the ADCON0 register

ADERR0, ADERR1, ADTCSF, ADSTT0, ADSTT1, ADSTRT0 a

n

fl

n

n

h

ADST flag: Bit 6 in the ADCON0 register

ADERR0, ADERR1, ADTCSF, ADSTT0, ADSTT1, ADSTRT0 and ADSTRT1 flag: bits 0, 1, 3, 4, 5, 6 and 7 in the ADSTAT0 register

ADST flag

ADERR0 flag

ADERR1 flag

ADTCSF flag

ADSTT0 flag

ADSTT1 flag

ADSTRT0 flag

ADSTRT1 flag

IR bit in the ADIC

register

ADST flag

ADERR0 flag

ADERR1 flag

ADTCSF flag

ADSTT0 flag

ADSTT1 flag

ADSTRT0 flag

ADSTRT1 flag

IR bit in the ADIC

register

Timer B0 underflow

Timer B0 underflow

Timer B1 underflow

Timer B1 underflow

Timer B1 underflow

•Example 3: When Timer B0 underflow is generated during A/D pin conversion of any pins except AN0 pin

•Example 4: After Timer B0 underflow is generated and when Timer B0 underflow is generated again

before Timer B1 underflow is genetaed

Loading...

Loading...