16. MULTI-MASTER I

2

C bus INTERFACE

puorG92/C61M

page 263

854fo7002,03.raM21.1.veR

2110-1010B90JER

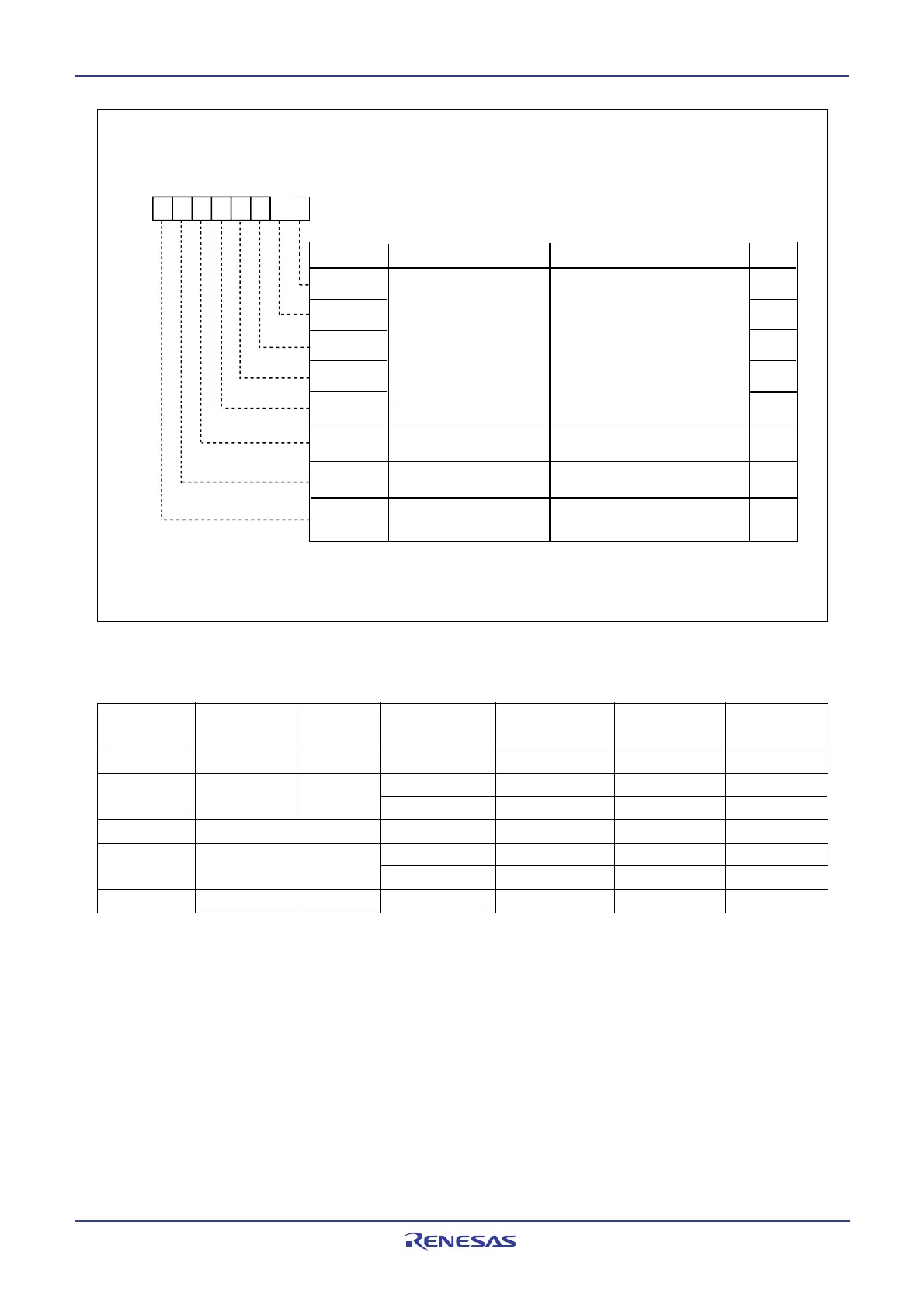

Figure 16.8 S2D0 Register

NOTES:

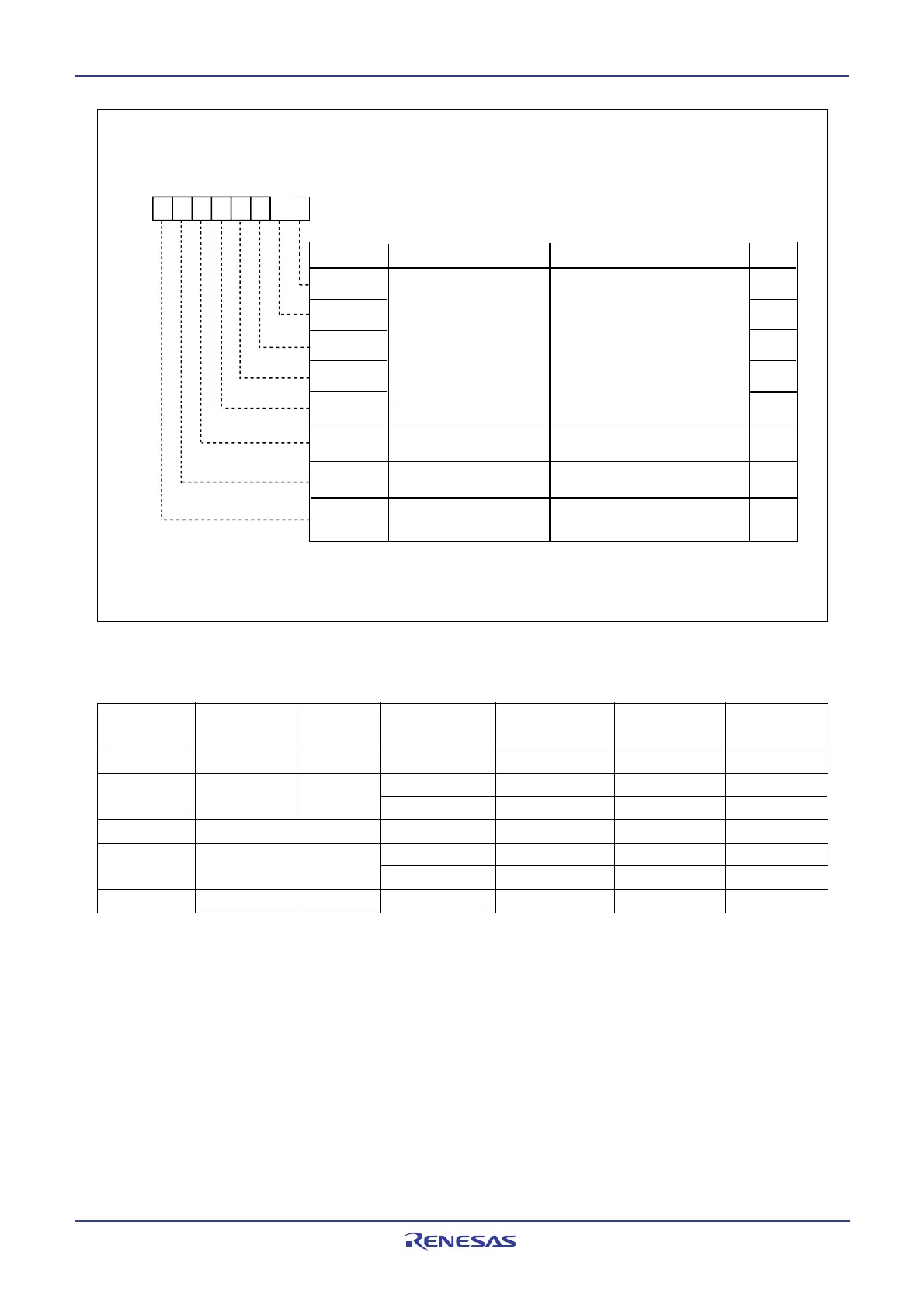

1. Do not set odd values or 000002 to START/STOP condition setting bits (SSC4 to SSC0)

2. When the PCLK0 bit in the PCLKR register is set to 1.

Oscillation I

2

C bus system

I

2

C bus system

SSC4-SSC0

(1)

SCL release Setup time Hold time

f1 (MHz) clock select

clock(MHz)

time (cycle) (cycle) (cycle)

10 1 / 2f1

(2)

5 XXX11110 6.2 µs (31) 3.2 µs (16) 3.0 µs (15)

8 1 / 2f1

(2)

4 XXX11010 6.75 µs(27) 3.5 µs (14) 3.25 µs(13)

XXX11000 6.25 µs(25) 3.25 µs (13) 3.0 µs (12)

8 1 / 8f1

(2)

1 XXX00100 5.0 µs (5) 3.0 µs (3) 2.0 µs (2)

4 1 / 2f1

(2)

2 XXX01100 6.5 µs (13) 3.5 µs (7) 3.0 µs (6)

XXX01010 5.5 µs (11) 3.0 µs (6) 2.5 µs (5)

2 1 / 2f1

(2)

1 XXX00100 5.0 µs (5) 3.0 µs (3) 2.0 µs (2)

Table 16.2 Recommended setting (SSC4-SSC0) start/stop condition at each oscillation frequency

0: Short setup/hold time mode

1: Long setup/hold time mode

0: S

DA enabled

1: S

CL enabled

0: Active in falling edge

1: Active in rising edge

START/STOP condition

generation select bit

S

CL/SDA interrupt pin

select bit

S

CL/SDA interrupt pin

polarity select bit

START/STOP condition

setting bits

(1)

STSPSEL

SIS

SIP

SSC4

SSC3

SSC2

SSC1

SSC0

FunctionBit NameBit Symbol

00011010

2

After Reset

02E5

16

AddressSymbol

S2D0

0

tart/stop

ondition

ontrol Re

isterI

2

RW

7

4

2b1b0

NOTE:

1. Do not set 00000

2 or odd values.

RW

RW

RW

RW

RW

RW

RW

RW

Setting for detection condition

of START/STOP condition.

See Table 16.2

Loading...

Loading...