7. Clock Generation Circuit

page 57

854fo7002,03.raM21.1.veR

2110-1010B90JER

puorG92/C61M

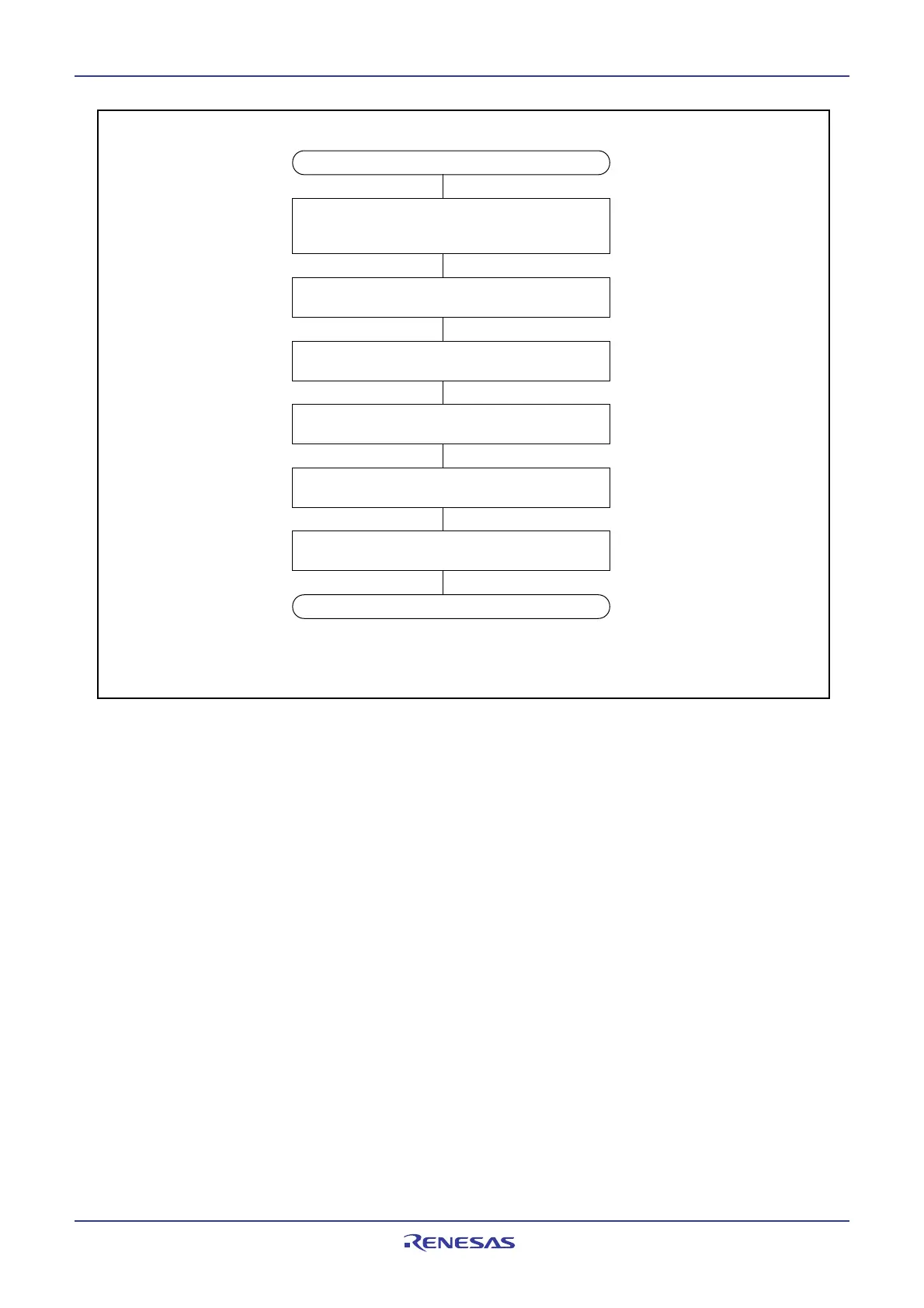

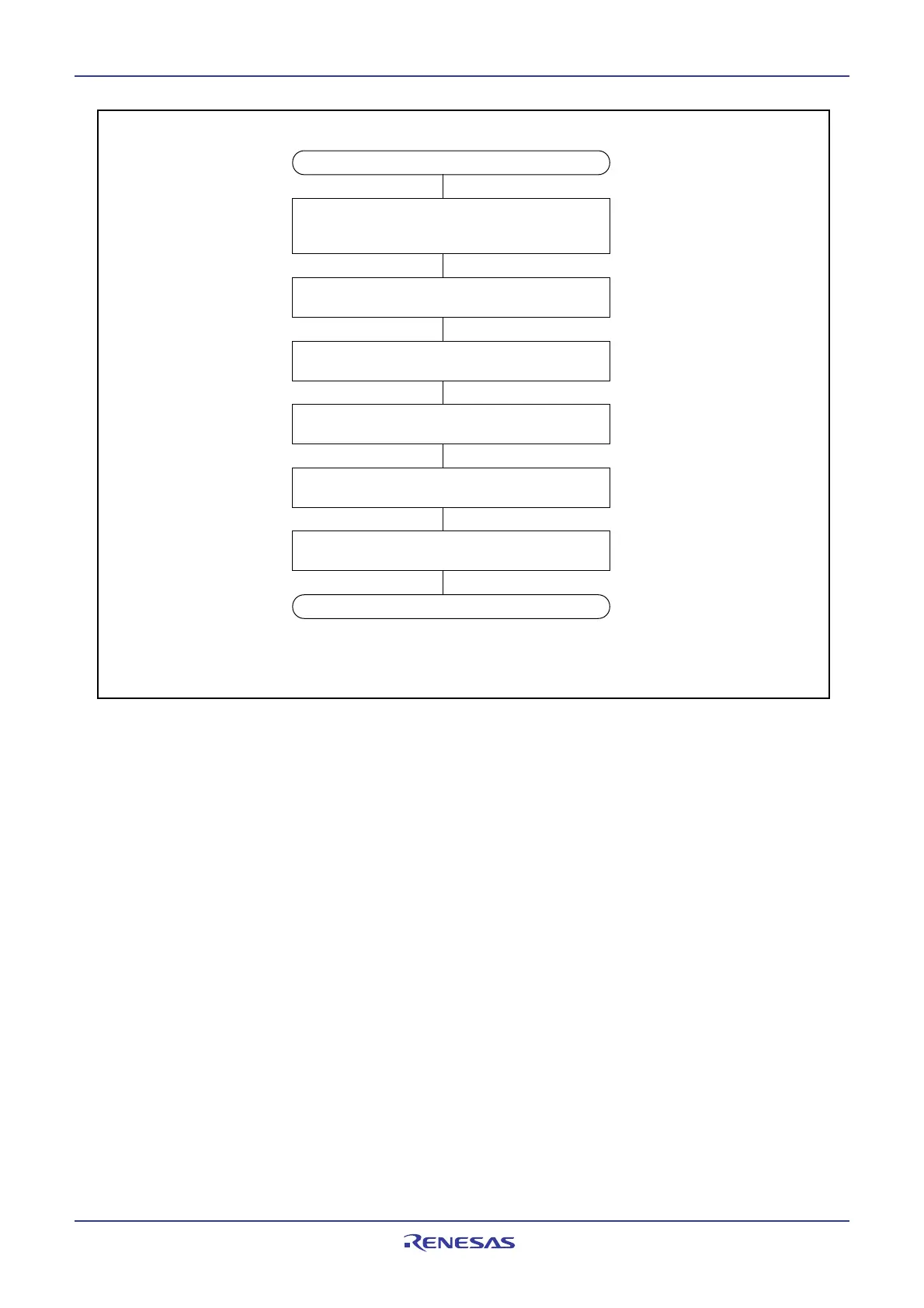

Figure 7.10 Procedure to Use PLL Clock as CPU Clock Source

START

Set the CM07 bit to 0 (main clock), bits CM17 and CM16 to

00

2(main clock undivided), and the CM06 bit to 0

(bits CM17 and CM16 enabled).

(1)

Set bits PLC02 to PLC00 (multiplying factor).

(To select a 16 MHz or higher PLL clock)

Set the PM20 bit to 0 (2-wait states).

Set the PLC07 bit to 1 (PLL operation).

Wait until the PLL clock becomes stable (tsu(PLL)).

Set the CM11 bit to 1 (PLL clock for the CPU clock source).

END

NOTE:

1. PLL operation mode can be entered from high speed mode.

Loading...

Loading...