UART0 to UART2

M30240 Group

Rev.1.00 Sep 24, 2003 Page 92 of 360

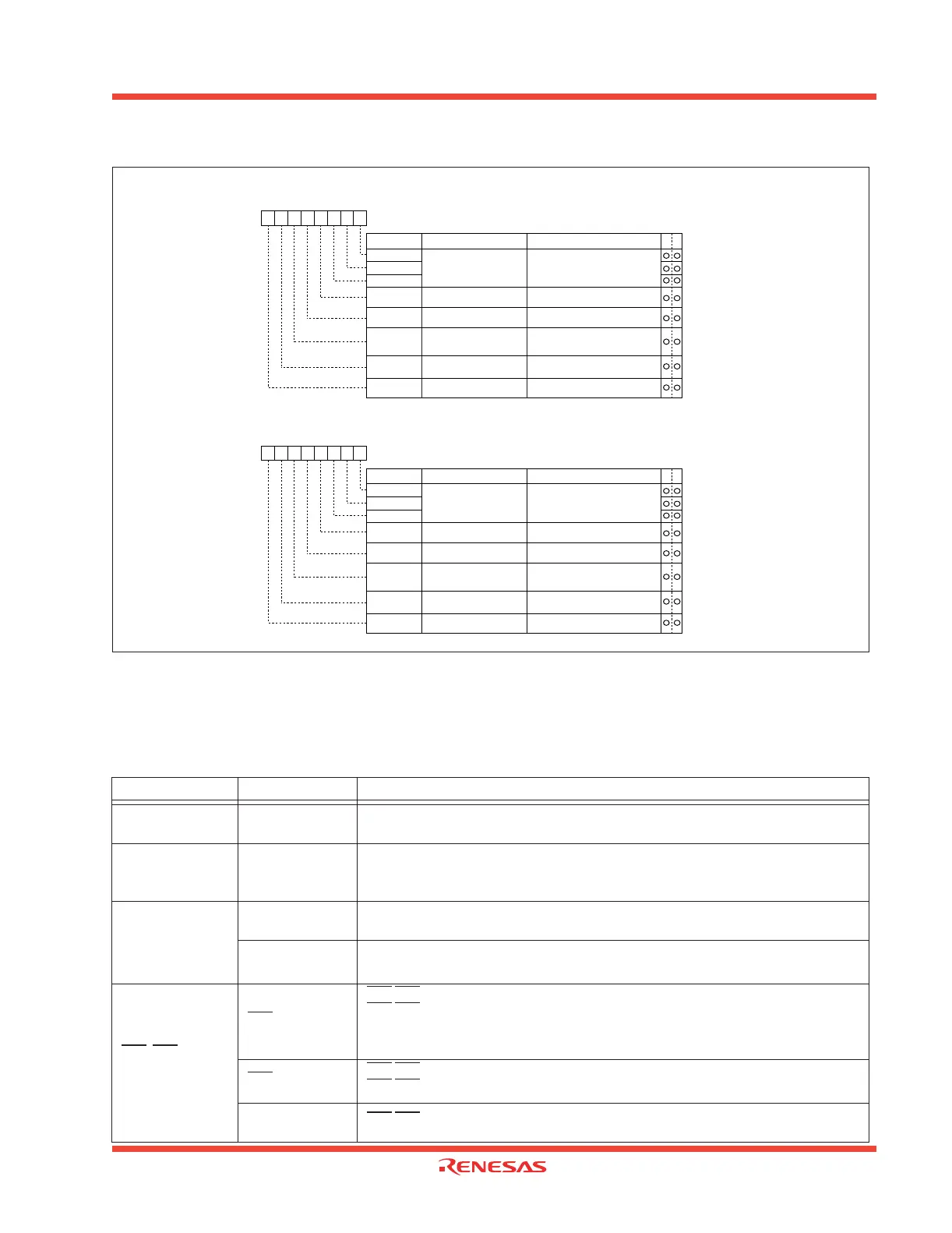

Figure 1.87: UARTi transmit/receive mode register.

Table 1.28 lists the functions of the input/output pins during UART mode. Note that for a period from

when the UARTi operation mode is selected to when transfer starts, the TxDi pin outputs a “H”.

Table 1.28: Input/output pin functions in UART mode

Pin name Function Method of selection

TxDi

(P6

3

, P6

7

, P7

0

)

Serial data

output

Outputs dummy data when performing reception.

RxDi

(P6

2

, P6

6

, P7

1

)

Serial data input

Port P6

2

, P6

6

, and P7

1

direction register (bits 2 and 6 at address 03EE

16

bit 1 at address

03EF

16

)= “0”

(Can be used as an input port when performing transmission only.)

CLKi

(P6

1

, P6

5

, P7

2

)

Programmable I/

O port

Internal/external clock select bit (bit 3 at address 03A0

16

, 03A8

16

, 0378

16

) = “0”

Transfer clock

input

Internal/external clock select bit (bit 3 at address 03A0

16

, 03A8

16

) = “1”

Port P6

1

, P6

5

direction register (bits 1 and 5 at address 03EE

16

) = “0”

CTS

i/RTSi

(P6

0

,P6

4

,P7

3

)

CTS

input

CTS

/RTS disable bit (bit 4 at address 03A4

16

, 03AC

16

, 037C

16

) = “0”

CTS

/RTS function select bit (bit 2 at address 03A4

16

, 03AC

16

, 037C

16

) = “0”

Port P60, P64 and P73 direction register (bits 0 and 4 at address 03EE

16

, bit 3 at address

03EF

16

) = “0”

RTS

output

CTS

/RTS disable bit (bit 4 at address 03A4

16

, 03AC

16

, 037C

16

) = “0”

CTS

/RTS function select bit (bit 2 at address 03A4

16

, 03AC

16

, 037C

16

) = “1”

Programmable I/

O port

CTS

/RTS disable bit (bit 4 at address 03A4

16

, 03AC

16

, 037C

16

) = “1”

Symbol Address When reset

UiMR(i=0,1) 03A0

16, 03A816 0016

CKDIR

UARTi transmit / receive mode registers

Internal / external clock

select bit

STPS

PRY

PRYE

SLEP

0 : Internal clock

1 : External clock (Note)

Bit name FunctionBit symbol

WR

b7 b6 b5 b4 b3 b2 b1 b0

SMD0

SMD1

SMD2

Serial I/O mode select bit

b2 b1 b0

0 : One stop bit

1 : Two stop bits

0 : Parity disabled

1 : Parity enabled

0 : Sleep mode deselected

1 : Sleep mode selected

1 0 0 : Transfer data 7 bits long

1 0 1 : Transfer data 8 bits long

1 1 0 : Transfer data 9 bits long

Valid when bit 6 = “1”

0 : Odd parity

1 : Even parity

Stop bit length select bit

Odd / even parity

select bit

Parity enable bit

Sleep select bit

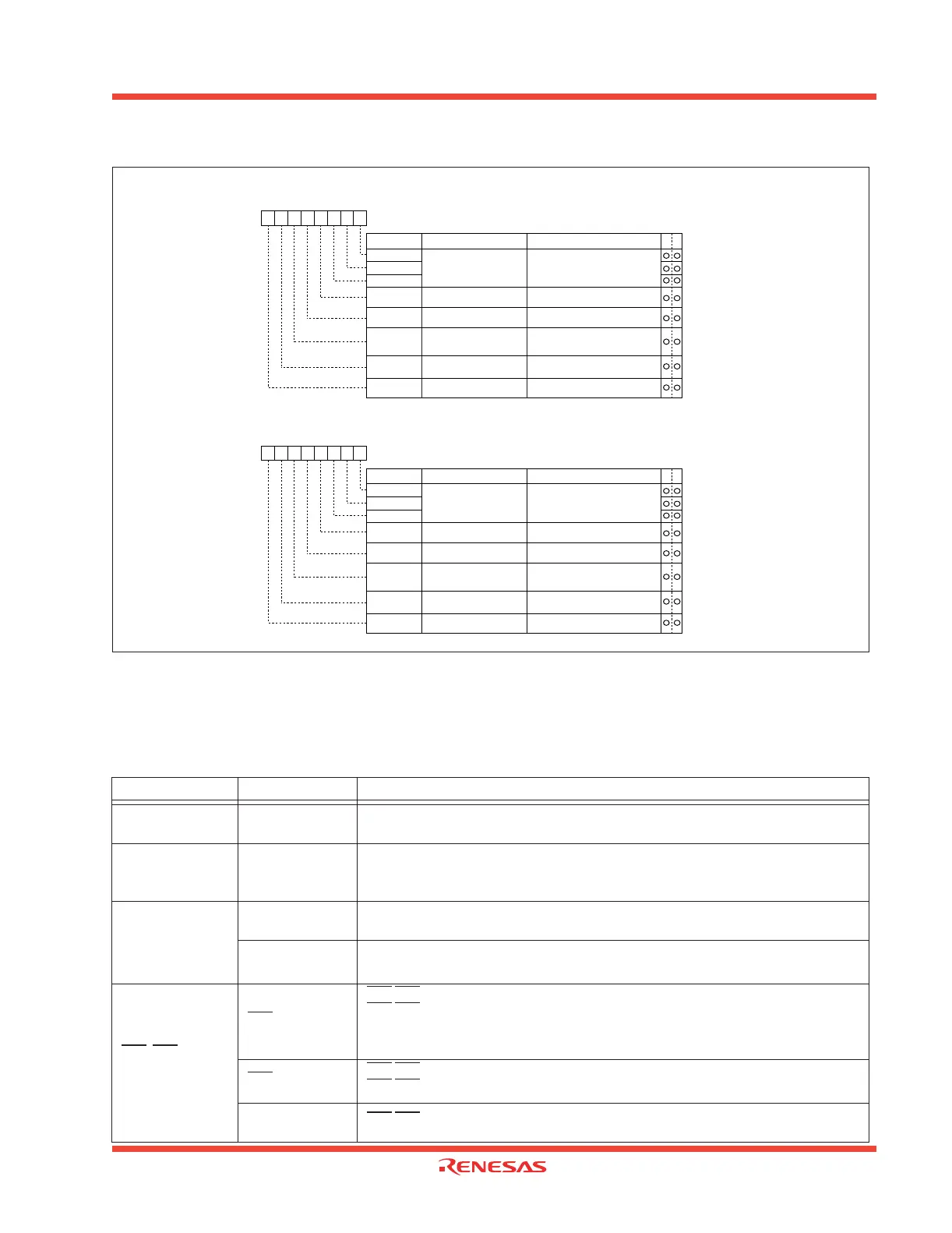

Symbol Address When reset

U2MR 0378

16 0016

CKDIR

UART2 transmit / receive mode register

Internal / external clock

select bit

STPS

PRY

PRYE

IOPOL

Must always be fixed to “0”

Bit name FunctionBit symbol

WR

b7 b6 b5 b4 b3 b2 b1 b0

SMD0

SMD1

SMD2

Serial I/O mode select bit

b2 b1 b0

0 : One stop bit

1 : Two stop bits

0 : Parity disabled

1 : Parity enabled

0 : No reverse

1 : Reverse

1 0 0 : Transfer data 7 bits long

1 0 1 : Transfer data 8 bits long

1 1 0 : Transfer data 9 bits long

Valid when bit 6 = “1”

0 : Odd parity

1 : Even parity

Stop bit length select bit

Odd / even parity

select bit

Parity enable bit

TxD, RxD I/O polarity

reverse bit (Note)

Note: Usually set to “0”.

Note: Set the corresponding port direction register to "0".

Loading...

Loading...