Universal Serial Bus

M30240 Group

Rev.1.00 Sep 24, 2003 Page 45 of 360

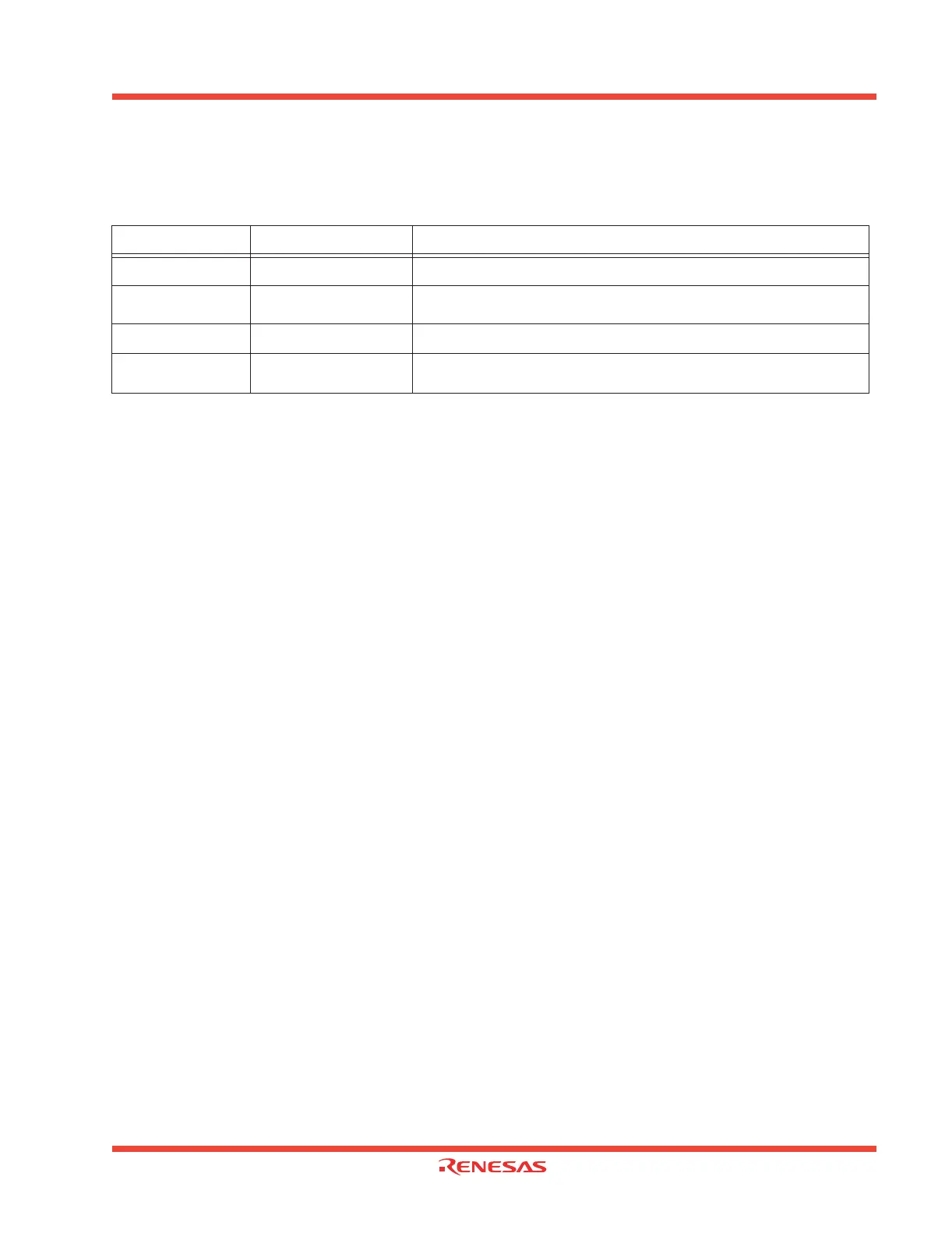

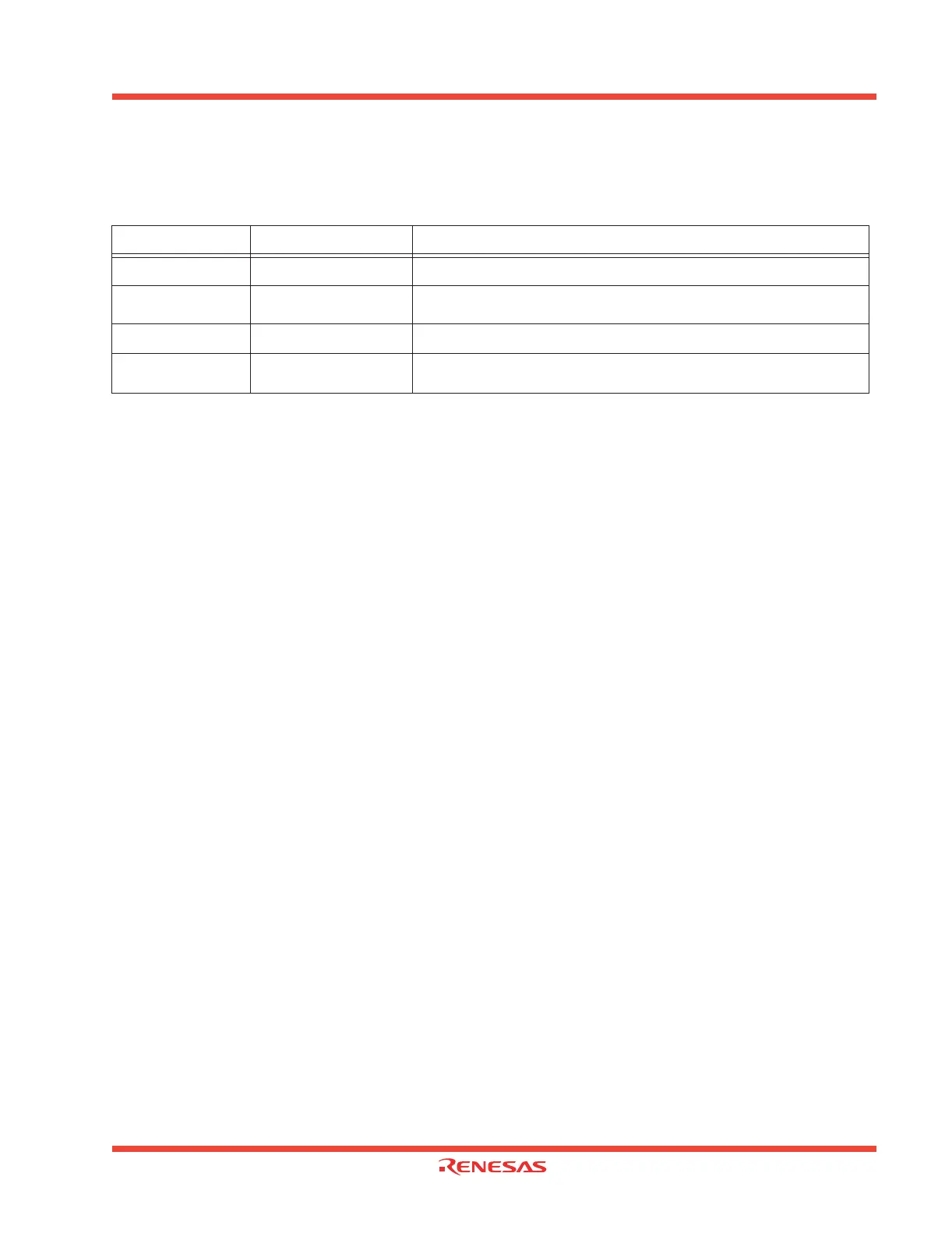

The status of endpoint 1-4 IN FIFOs for both of the above cases can be obtained from the IN CSR of the cor-

responding IN FIFO as shown in Table 1.14 .

1.2.18.3.2 Out (Receive) FIFOs

The USB FCU writes data to the endpoint’s OUT FIFO location specified by the FIFO write pointer, which au-

tomatically increments by one after a write. When the USB FCU has successfully received a data packet, it

sets the OUT_PKT_RDY bit of the corresponding OUT CSR to a “1”. The CPU/DMAC should only read data

from the OUT FIFO when the OUT_PKT_RDY bit of the OUT CSR is a “1”.

• Endpoint 0 OUT FIFO Operation:

The USB FCU sets the OUT_PKT_RDY bit to a “1” after it has successfully received a packet of data from the

host. The CPU sets bit SERVICED_OUT_PKT_RDY to a “1” to clear the OUT_PKT_RDY bit after the packet

of data has been unloaded from the OUT FIFO by the CPU.

• Endpoint 1-4 OUT FIFO Operation when AUTO_CLR (bit 7 of Endpoint x OUT CSR) = “0” (disabled):

MAXP > 1/2 of the OUT FIFO size: The USB FCU sets the OUT_PKT_RDY bit of the associated IN CSR to

a “1” after it has successfully received a packet of data from the host. The CPU writes a “0” to the

OUT_PKT_RDY bit after the packet of data has been unloaded from the OUT FIFO by the CPU/DMAC.

MAXP <= 1/2 of the OUT FIFO size: The USB FCU sets the OUT_PKT_RDY bit of the associated IN CSR to

a “1” after it has successfully received a packet of data from the host. The CPU writes a “0” to the

OUT_PKT_RDY bit after the packet of data has been unloaded from the OUT FIFO by the CPU/DMAC. If an-

other packet is in the OUT FIFO, the OUT_PKT_RDY bit will be set to a “1” again almost immediately (such

that it may appear that the OUT_PKT_RDY bit remains a “1”). In this configuration, the FIFO can store up to

two data packets at the same time for back-to-back reception.

• Endpoint 1-4 OUT FIFO Operation when AUTO_CLR (bit 7 of Endpoint x OUT CSR) = “1” (enabled):

MAXP > 1/2 of the OUT FIFO size: The USB FCU sets the OUT_PKT_RDY bit of the associated IN CSR to

a “1” after it has successfully received a packet of data from the host. The USB FCU clears the

OUT_PKT_RDY bit to a “0” automatically when the number of bytes of data equal to the MAXP (maximum

packet size) has been unloaded from the OUT FIFO by the CPU/DMAC.

MAXP <= 1/2 of the OUT FIFO size: The USB FCU sets the OUT_PKT_RDY bit of the associated IN CSR to

a “1” after it has successfully received a packet of data from the host. The USB FCU clears the

OUT_PKT_RDY bit to a “0” automatically when the number of bytes of data equal to the MAXP (maximum

packet size) has been unloaded from the OUT FIFO by the CPU/DMAC. If another packet is in the OUT FIFO,

the OUT_PKT_RDY bit will be set to a “1” again almost immediately (such that it may appear that the

OUT_PKT_RDY bit remains a “1”). In this configuration, the FIFO can store up to two data packets at the same

time for back-to-back reception.

A software flush causes the USB FCU to act as if a packet has been unloaded from the OUT FIFO. If there is

one packet in the OUT FIFO, a flush will cause the OUT FIFO to be empty. If there are two packets in the OUT

FIFO, a flush will cause the older packet to be flushed out from the OUT FIFO.

Table 1.14: TA FIFO Status

IN_PKT_RDY TX_NOT_EPT IN FIFO Status

00

No data packet in IN FIFO

01

One data packet in IN FIFO if MAXP <= 1/2 of the FIFO size./

Invalid when MAXP>1/2 of the FIFO size

10

Invalid

11

Two data packets in IN FIFO when MAXP <=1/2 of the FIFO size

One data packet in IN FIFO when MAXP > 1/2 of the FIFO size

Loading...

Loading...