PM0215 The STM32 Cortex-M0 processor

Doc ID 022979 Rev 1 19/91

2.2.1 Memory regions, types and attributes

The memory map is split into regions. Each region has a defined memory type, and some

regions have additional memory attributes. The memory type and attributes determine the

behavior of accesses to the region.

The memory types are:

The different ordering requirements for Device and Strongly-ordered memory mean that the

memory system can buffer a write to Device memory, but must not buffer a write to Strongly-

ordered memory.

Additional memory attributes include:

2.2.2 Memory system ordering of memory accesses

For most memory accesses caused by explicit memory access instructions, the memory

system does not guarantee that the order in which the accesses complete matches the

program order of the instructions, providing this does not affect the behavior of the

instruction sequence. Normally, if correct program execution depends on two memory

accesses completing in program order, software must insert a memory barrier instruction

between the memory access instructions, see Section 2.2.4: Software ordering of memory

accesses on page 20.

However, the memory system does guarantee some ordering of accesses to Device and

Strongly-ordered memory. For two memory access instructions A1 and A2, if A1 occurs

before A2 in program order, the ordering of the memory accesses caused by two

instructions is:

Normal The processor can re-order transactions for efficiency, or

perform speculative reads.

Device The processor preserves transaction order relative to other

transactions to Device or Strongly-ordered memory.

Strongly-ordered The processor preserves transaction order relative to all other

transactions.

Execute Never (XN) Means the processor prevents instruction accesses. Any

attempt to fetch an instruction from an XN region causes a

HardFault exception.

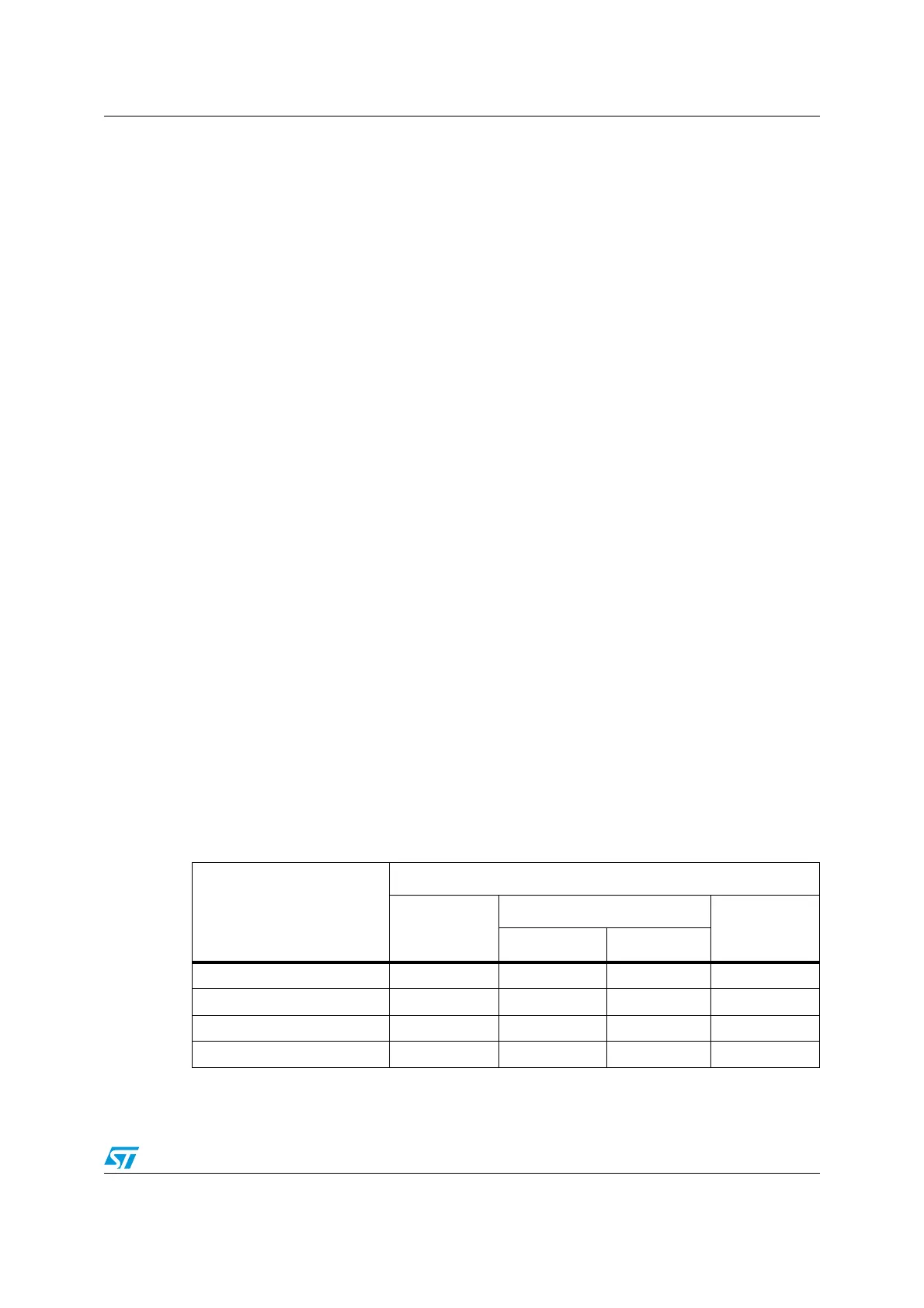

Table 10. Ordering of memory accesses

(1)

1. - means that the memory system does not guarantee the ordering of the accesses.

< means that accesses are observed in program order, that is, A1 is always observed before A2.

A1

A2

Normal access

Device access Strongly

ordered

access

Non-shareable Shareable

Normal access - - - -

Device access, non-shareable - < - <

Device access, shareable - - < <

Strongly ordered access - < < <

Loading...

Loading...