PM0215 The STM32 Cortex-M0 processor

Doc ID 022979 Rev 1 21/91

Use memory barrier instructions in, for example:

● Vector table: If the program changes an entry in the vector table, and then enables the

corresponding exception, use a DMB instruction between the operations. This ensures

that if the exception is taken immediately after being enabled the processor uses the

new exception vector.

● Self-modifying code: If a program contains self-modifying code, use an ISB

instruction immediately after the code modification in the program. This ensures

subsequent instruction execution uses the updated program.

● Memory map switching: If the system contains a memory map switching mechanism,

use a DSB instruction after switching the memory map in the program. This ensures

subsequent instruction execution uses the updated memory map.

Memory accesses to Strongly-ordered memory, such as the system control block, do not

require the use of DMB instructions.

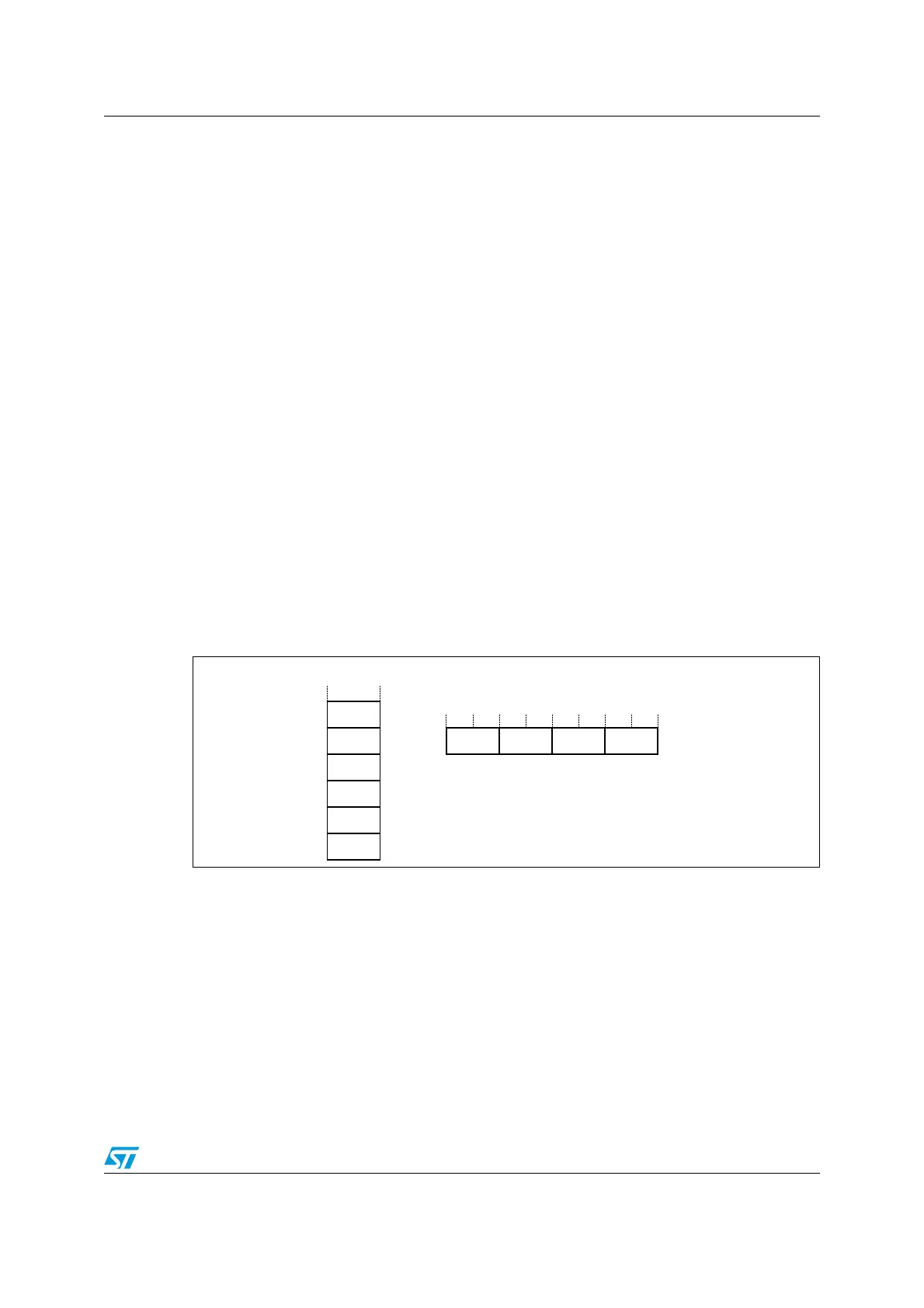

2.2.5 Memory endianness

The processor views memory as a linear collection of bytes numbered in ascending order

from zero. For example, bytes 0-3 hold the first stored word, and bytes 4-7 hold the second

stored word.

Little-endian format

In little-endian format, the processor stores the least significant byte (lsbyte) of a word at the

lowest-numbered byte, and the most significant byte (msbyte) at the highest-numbered byte.

See Figure 7 for an example.

Figure 7. Little-endian example

0HPRU\ 5HJLVWHU

$GGUHVV$

$

OVE\WH

PVE\WH

$

$

%%% %

%

%

%

%

Loading...

Loading...