Core peripherals PM0215

80/91 Doc ID 022979 Rev 1

4.3.3 Application interrupt and reset control register (AIRCR)

Address offset: 0x0C

Reset value: 0xFA05 0000

The AIRCR provides endian status for data accesses and reset control of the system.

To write to this register, you must write 0x5FA to the VECTKEY field, otherwise the

processor ignores the write.

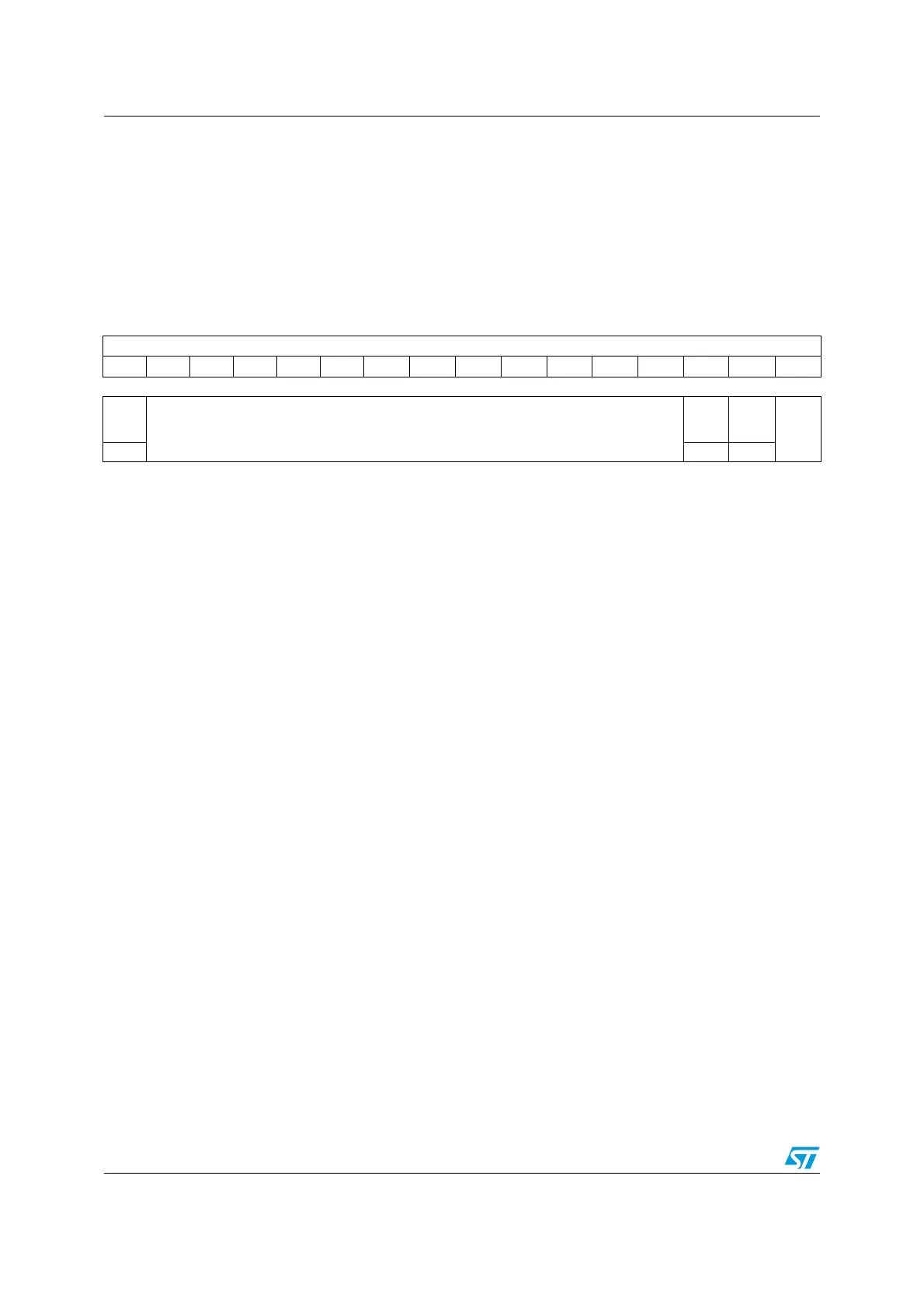

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved(read)/ VECTKEY[15:0](write)

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

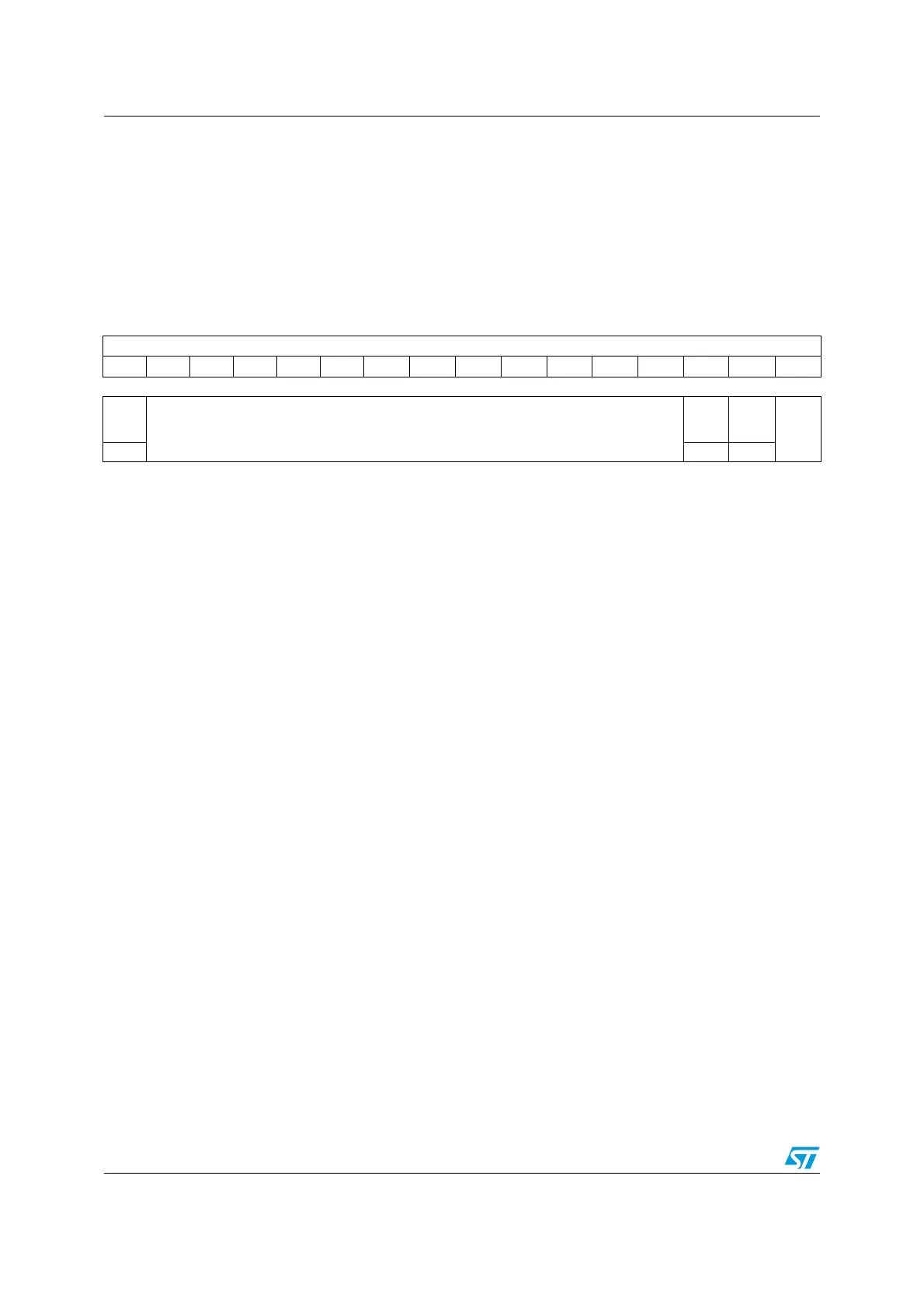

1514131211109876543210

ENDIA

NESS

Reserved

SYS

RESET

REQ

VECT

CLR

ACTIVE

Reserv

ed

r ww

Bits 31:16 Reserved / VECTKEY Register key

Reads as unknown

On writes, write 0x5FA to VECTKEY, otherwise the write is ignored.

Bit 15 ENDIANESS Data endianness bit

Reads as 0.

0: Little-endian

Bits 14:3 Reserved, must be kept cleared

Bit 2 SYSRESETREQ System reset request

Reads as 0.

0: No system reset request

1: Asserts a signal to the outer system that requests a reset.

Bit 1 VECTCLRACTIVE

Reserved for Debug use. This bit reads as 0. When writing to the register you must write 0 to

this bit, otherwise behavior is unpredictable.

Bit 0 Reserved, must be kept cleared

Loading...

Loading...