PM0215 The STM32 Cortex-M0 instruction set

Doc ID 022979 Rev 1 61/91

3.7 Miscellaneous instructions

Tabl e 23 shows the remaining Cortex-M0 instructions:

3.7.1 BKPT

Breakpoint.

Syntax

BKPT #imm

where: ‘imm’ is an integer in the range 0-255.

Operation

BKPT causes the processor to enter Debug state. Debug tools can use this to investigate

system state when the instruction at a particular address is reached.

imm is ignored by the processor. If required, a debugger can use it to store additional

information about the breakpoint.

The processor might produce a HardFault or go in to lockup if a debugger is not attached

when a BKPT instruction is executed. See Lockup on page 28 for more information.

Restrictions: None

Condition flags

This instruction does not change the flags.

Examples

BKPT #0 ; Breakpoint with immediate value set to 0x0.

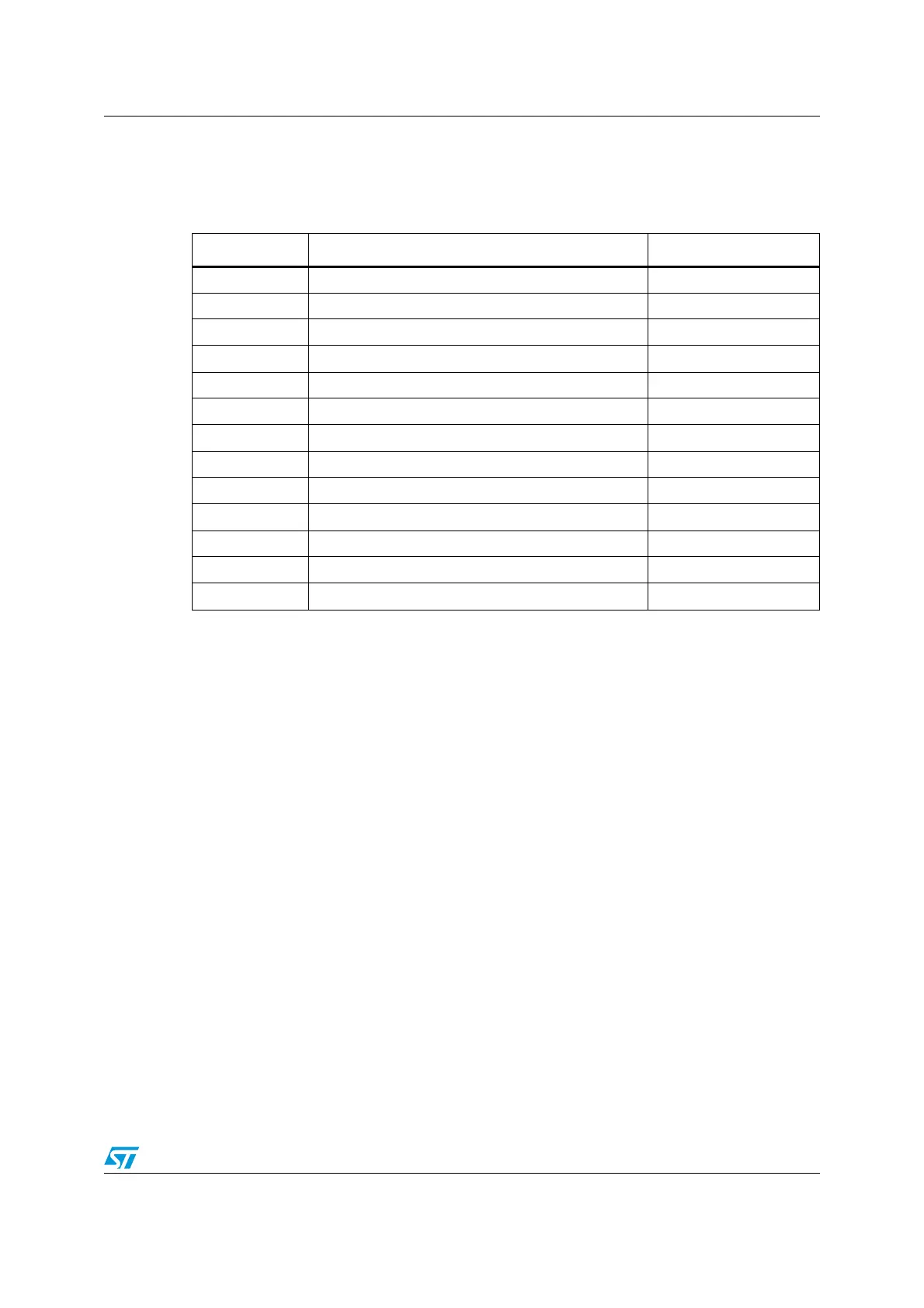

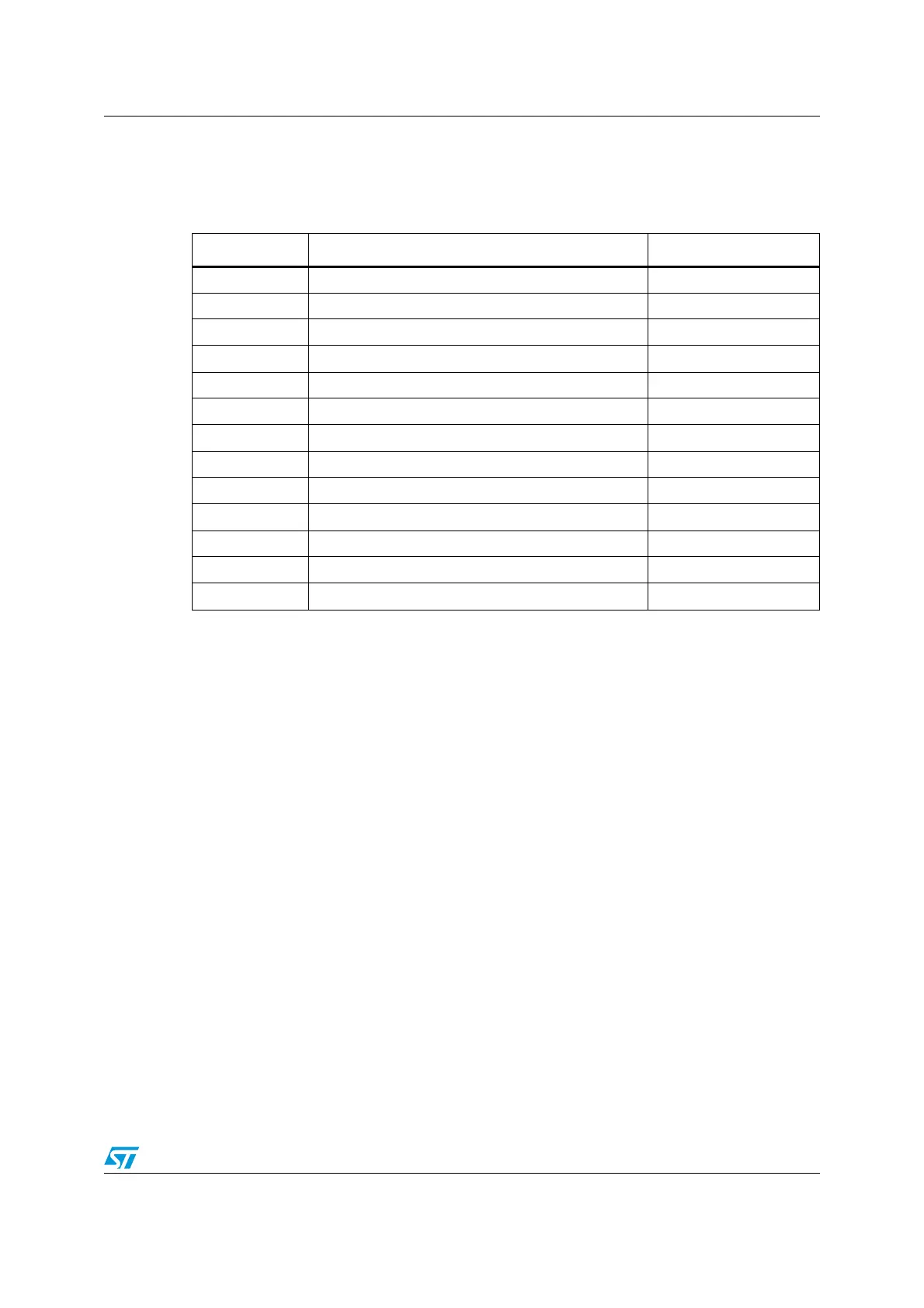

Table 23. Miscellaneous instructions

Mnemonic Brief description See

BKPT Breakpoint BKPT on page 61

CPSID Change Processor State, Disable Interrupts CPSID CPSIE on page 62

CPSIE Change Processor State, Enable Interrupts CPSID CPSIE on page 62

DMB Data Memory Barrier DMB on page 63

DSB Data Synchronization Barrier DSB on page 63

ISB Instruction Synchronization Barrier ISB on page 64

MRS Move from special register to register MRS on page 64

MSR Move from register to special register MSR on page 65

NOP No Operation NOP on page 66

SEV Send Event SEV on page 66

SVC Supervisor Call SVC on page 67

WFE Wait For Event WFE on page 67

WFI Wait For Interrupt WFI on page 68

Loading...

Loading...