PM0215 The STM32 Cortex-M0 instruction set

Doc ID 022979 Rev 1 59/91

3.6 Branch and control instructions

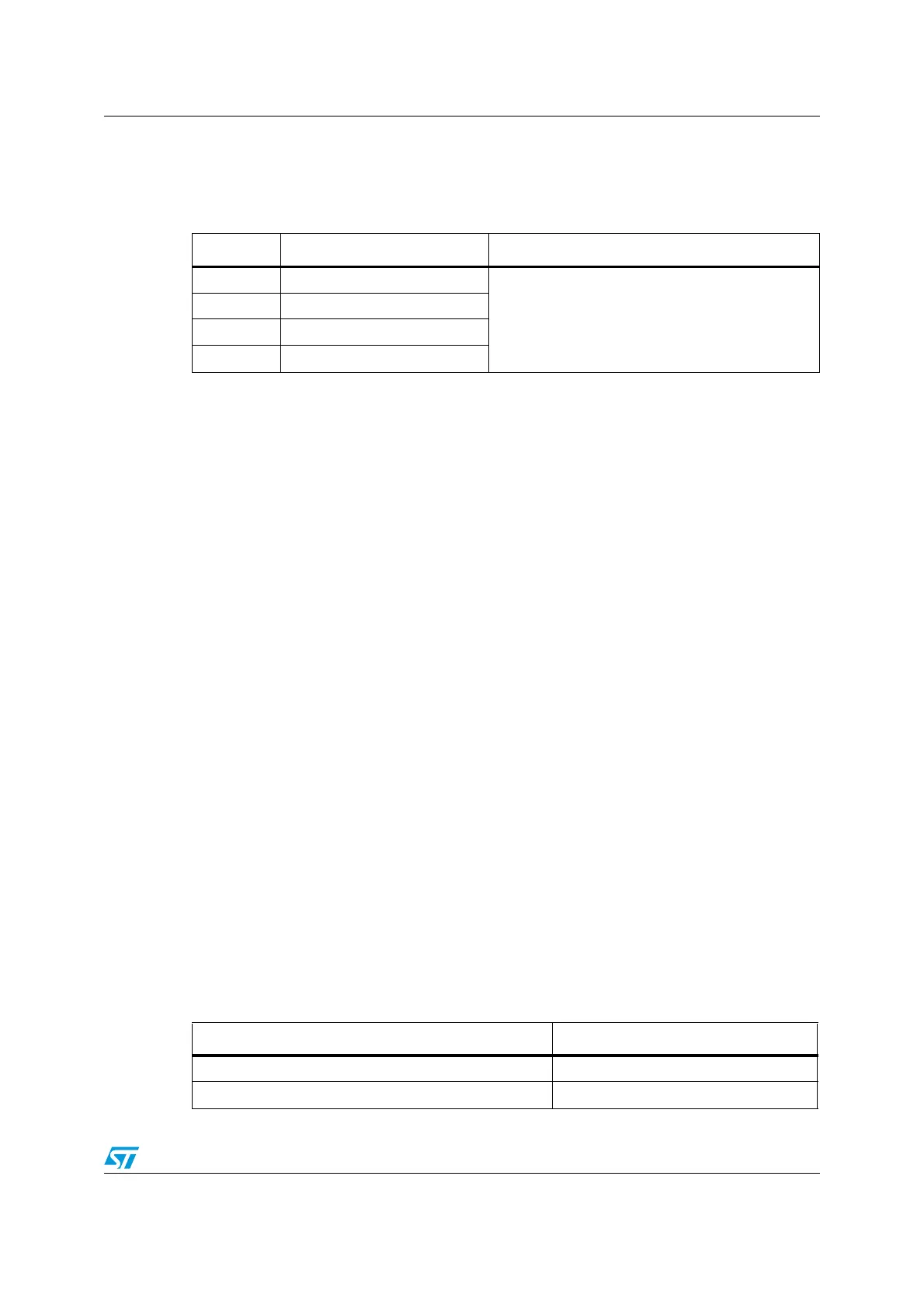

Tabl e 21 shows the branch and control instructions:

3.6.1 B, BL, BX, and BLX

Branch instructions.

Syntax

B{cond} label

BL label

BX Rm

BLX Rm

where:

● ‘B’ is branch (immediate).

● ‘BL’ is branch with link (immediate).

● ‘BX’ is branch indirect (register).

● ‘BLX’ is branch indirect with link (register).

● ‘label’ is a PC-relative expression. See PC-relative expressions on page 39.

● ‘Rm’ is a register that indicates an address to branch to.

● ’Cond’ is an optional condition code, see Conditional execution on page 39.

Operation

All these instructions cause a branch to label, or to the address indicated in Rm. In addition:

● The BL and BLX instructions write the address of the next instruction to LR (the link

register, R14).

● The BX and BLX instructions cause a Hard fault exception if bit[0] of Rm is 0.

● The BL and BLX instructions also set bit[0] of the LR to 1. This ensures that the value is

suitable for use by a subsequent POP {PC} or BX instruction to perform a successful

return branch.

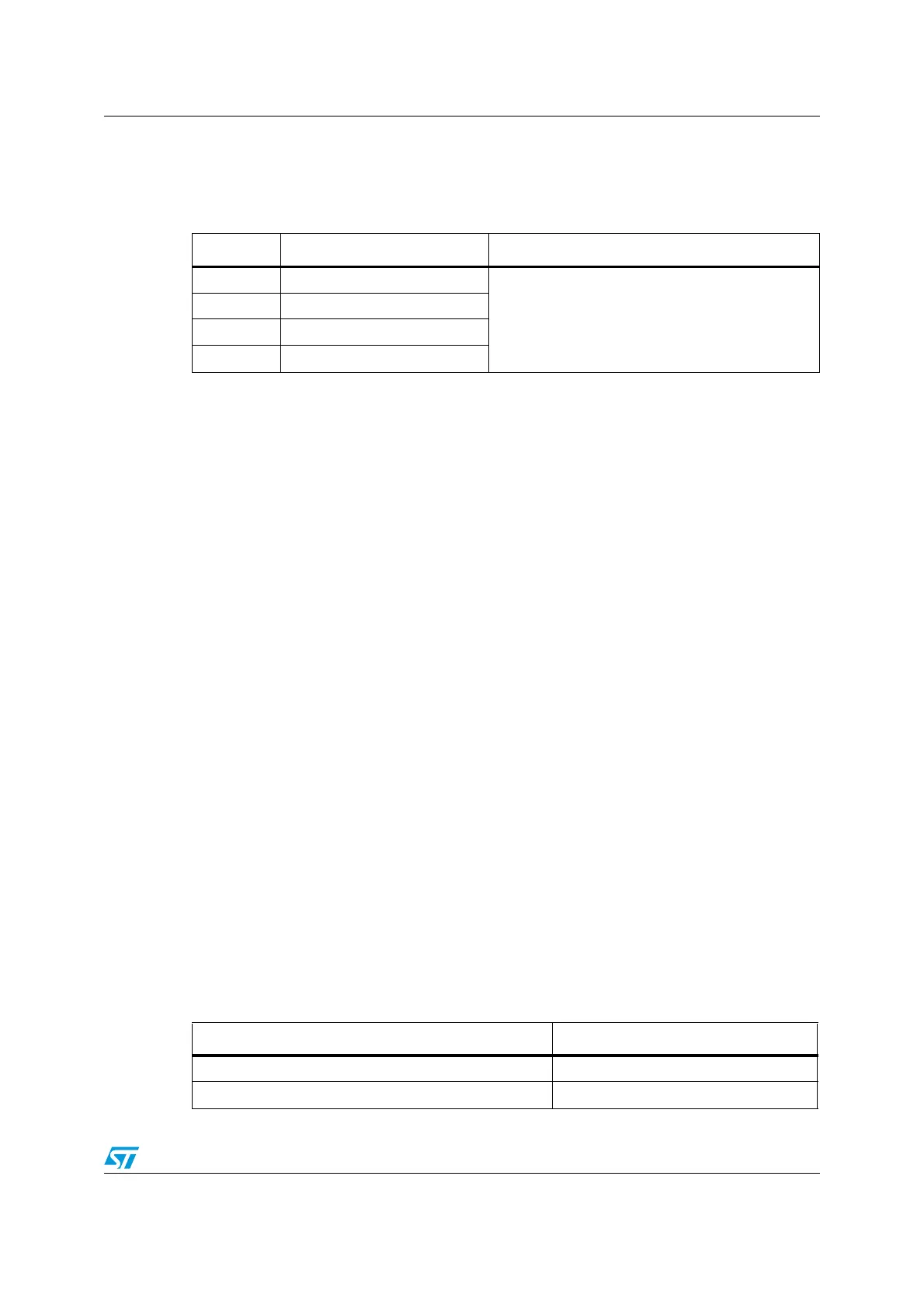

Tabl e 22 shows the ranges for the various branch instructions.

Table 21. Branch and control instructions

Mnemonic Brief description See

B{cc} Branch {conditionally}

B, BL, BX, and BLX on page 59

BL Branch with link

BLX Branch indirect with link

BX Branch indirect

Table 22. Branch ranges

Instruction Branch range

B label −2 KB to +2 KB

Bcond label − 256 bytes to +254 bytes

Loading...

Loading...