Core peripherals PM0215

84/91 Doc ID 022979 Rev 1

4.3.7 SCB usage hints and tips

Ensure software uses aligned 32-bit word size transactions to access all the system control

block registers.

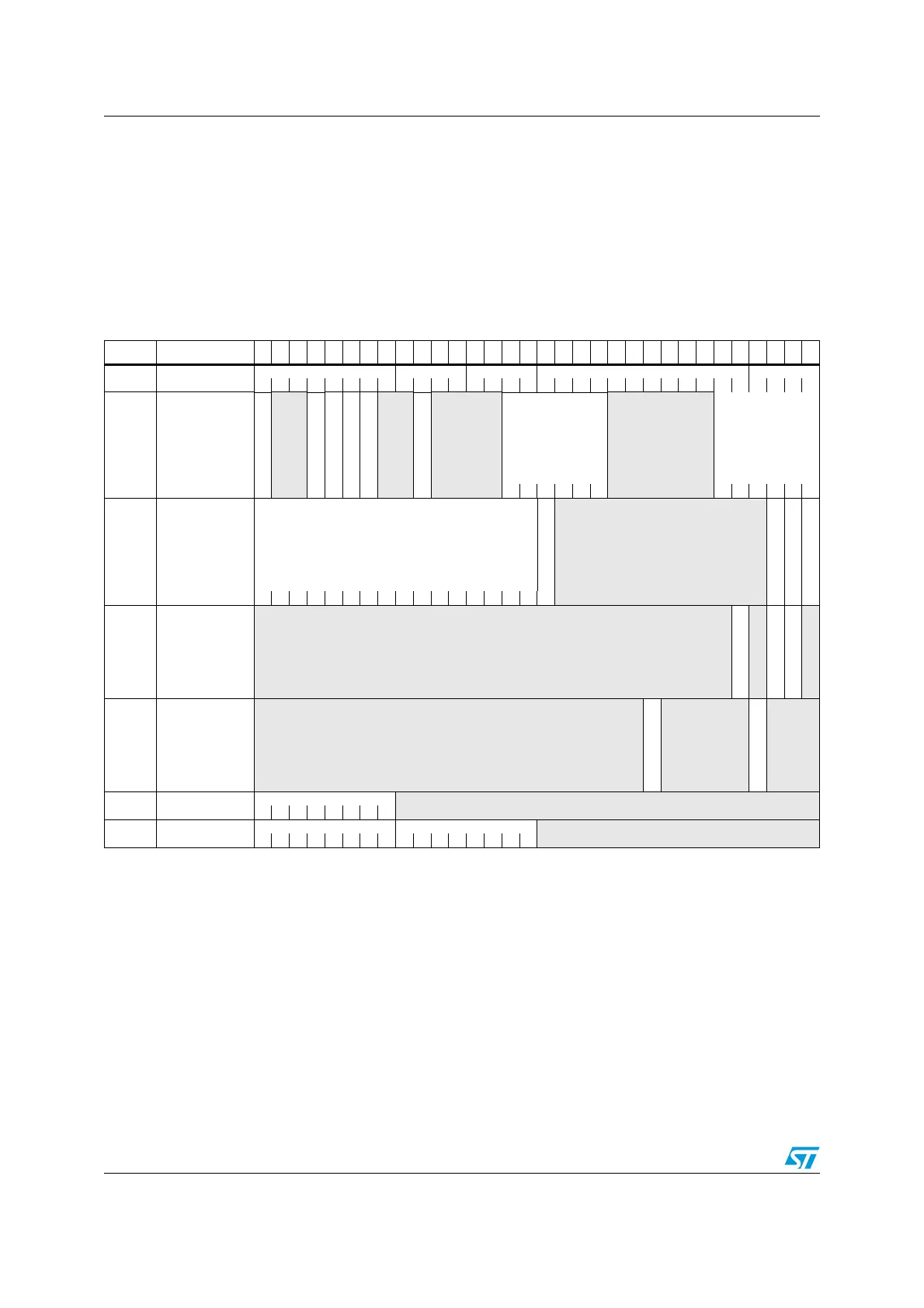

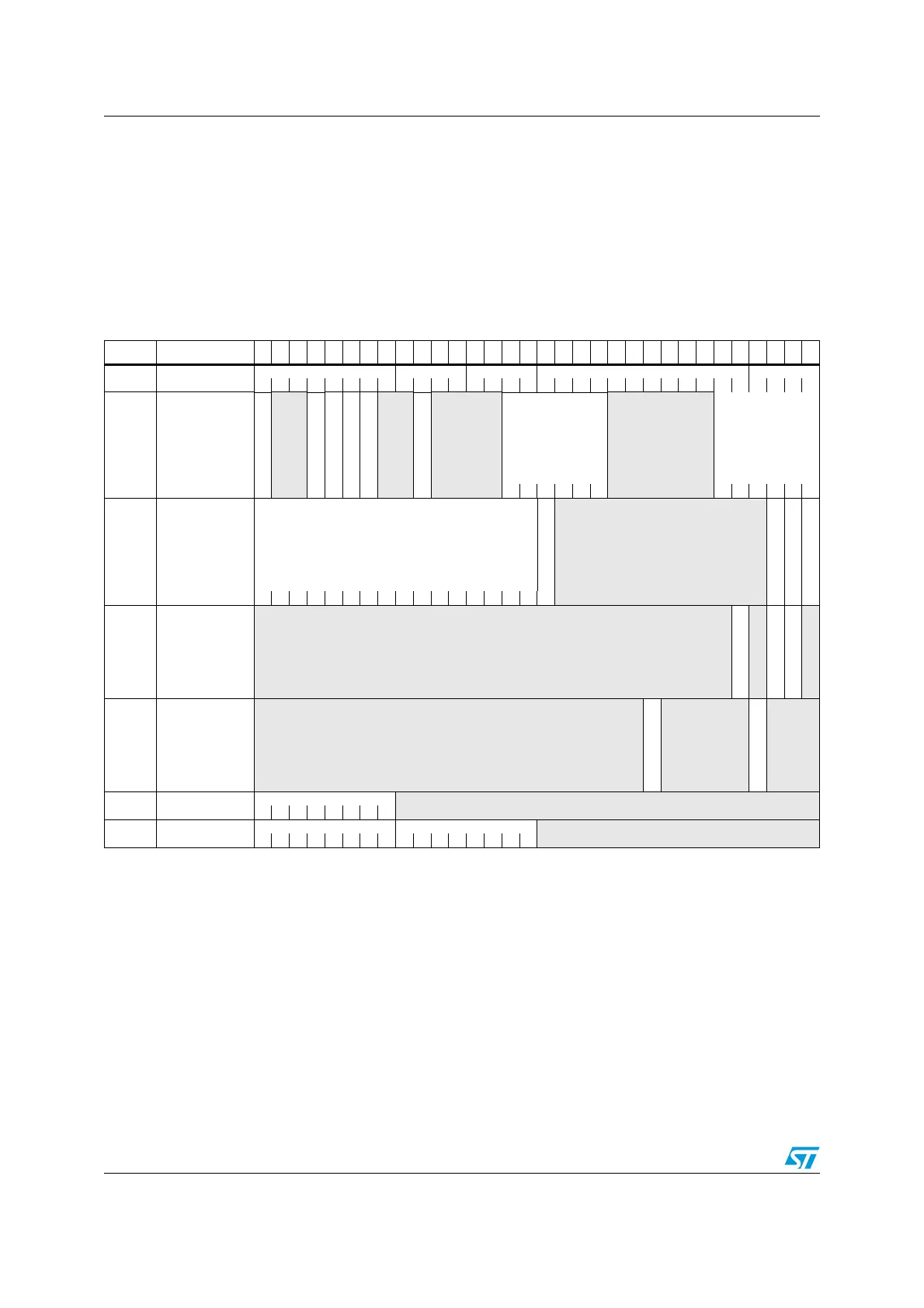

4.3.8 SCB register map

The table provides shows the System control block register map and reset values. The base

address of the SCB register block is 0xE000 ED00 for register described in Tabl e 3 2 .

Table 32. SCB register map and reset values

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x00

CPUID Implementer Variant Constant PartNo Revision

Reset Value 01000001000111111100001000110001

0x04

ICSR

NMIPENDSET

Reser

ved

PENDSVSET

PENDSVCLR

PENDSTSET

PENDSTCLR

Reser

ved

ISRPENDING

Reserved

VECTPENDING[5:0]

Reserved

VECTACTIVE[5:0]

Reset Value 0 0000 0 000000 000000

0x0C

AIRCR VECTKEY[15:0]

ENDIANESS

Reserved

SYSRESETREQ

VECTCLRACTIVE

VECTRESET

Reset Value 00000001111110100 000

0x10

SCR

Reserved

SEVONPEND

Reserved

SLEEPDEEP

SLEEPONEXIT

Reserved

Reset Value 000

0x14

CCR

Reserved

STKALIGN

Reserved

UNALIGN_TRP

Reserved

Reset Value 11

0x1C

SHPR2 PRI11

Reserved

Reset Value 00000000

0x20

SHPR3 PRI15 PRI14

Reserved

Reset Value 0000000000000000

Loading...

Loading...